SBAS181C - NOVEMBER 2001 - REVISED MARCH 2005

# 12-Bit, 8-Channel Sampling ANALOG-TO-DIGITAL CONVERTER with I<sup>2</sup>C<sup>™</sup> Interface

#### **FEATURES**

- **8-CHANNEL MULTIPLEXER**

- 50kHz SAMPLING RATE

- NO MISSING CODES

- 2.7V TO 5V OPERATION

- INTERNAL 2.5V REFERENCE

- I<sup>2</sup>C INTERFACE SUPPORTS: Standard, Fast, and High-Speed Modes

- **TSSOP-16 PACKAGE**

#### **APPLICATIONS**

- VOLTAGE-SUPPLY MONITORING

- ISOLATED DATA ACQUISITION

- TRANSDUCER INTERFACES

- BATTERY-OPERATED SYSTEMS

- REMOTE DATA ACQUISITION

## **DESCRIPTION**

The ADS7828 is a single-supply, low-power, 12-bit data acquisition device that features a serial I<sup>2</sup>C interface and an 8-channel multiplexer. The Analog-to-Digital (A/D) converter features a sample-and-hold amplifier and internal, asynchronous clock. The combination of an I<sup>2</sup>C serial, 2-wire interface and micropower consumption makes the ADS7828 ideal for applications requiring the A/D converter to be close to the input source in remote locations and for applications requiring isolation. The ADS7828 is available in a TSSOP-16 package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

I<sup>2</sup>C is a trademark of Koninklijke Philps Electronics N.V. All other trademarks are the property of their respective owners.

#### **ABSOLUTE MAXIMUM RATINGS(1)**

| +V <sub>DD</sub> to GND0.3V to ·                         | +6V            |

|----------------------------------------------------------|----------------|

| Digital Input Voltage to GND0.3V to +V <sub>DD</sub> + 0 | ).3V           |

| Operating Temperature Range40°C to +10                   | 5°C            |

| Storage Temperature Range65°C to +15                     | 0°C            |

| Junction Temperature (T <sub>J</sub> max)+15             | 0°C            |

| TSSOP Package                                            |                |

| Power Dissipation(T <sub>J</sub> max – T <sub>A</sub> )  | $/\theta_{JA}$ |

| $	heta_{JA}$ Thermal Impedance240°C                      | C/W            |

| Lead Temperature, Soldering                              |                |

| Vapor Phase (60s) +21                                    | 5°C            |

| Infrared (15s)+22                                        | 0°C            |

NOTE: (1) Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

## ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### PACKAGE/ORDERING INFORMATION(1)

| PRODUCT   | MAXIMUM<br>INTEGRAL<br>LINEARITY<br>ERROR (LSB) | PACKAGE-LEAD | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER             | TRANSPORT<br>MEDIA, QUANTITY              |

|-----------|-------------------------------------------------|--------------|-----------------------|-----------------------------------|--------------------------------|-------------------------------------------|

| ADS7828E  | ±2<br>"                                         | TSSOP-16     | PW<br>"               | -40°C to +85°C                    | ADS7828E/250<br>ADS7828E/2K5   | Tape and Reel, 250<br>Tape and Reel, 2500 |

| ADS7828EB | ±1<br>"                                         | TSSOP-16     | PW<br>"               | -40°C to +85°C                    | ADS7828EB/250<br>ADS7828EB/2K5 | Tape and Reel, 250<br>Tape and Reel, 2500 |

NOTE: (1) For the most current package and ordering information, see the Package Option Addendum at the end of this data sheet, or see the TI web site at www.ti.com.

#### **PIN CONFIGURATION**

| CH0 1 16 +V <sub>DD</sub>                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------|

| CH1 2 CH2 3 CH3 4 CH4 5 CH5 6 CH6 7 CH7 8  15 SDA 14 SCL 13 A1 12 A0 11 COM 10 REF <sub>IN</sub> /REF <sub>OUT</sub> 9 GND |

#### PIN DESCRIPTIONS

| PIN | NAME             | DESCRIPTION                                        |

|-----|------------------|----------------------------------------------------|

| 1   | CH0              | Analog Input Channel 0                             |

| 2   | CH1              | Analog Input Channel 1                             |

| 3   | CH2              | Analog Input Channel 2                             |

| 4   | CH3              | Analog Input Channel 3                             |

| 5   | CH4              | Analog Input Channel 4                             |

| 6   | CH5              | Analog Input Channel 5                             |

| 7   | CH6              | Analog Input Channel 6                             |

| 8   | CH7              | Analog Input Channel 7                             |

| 9   | GND              | Analog Ground                                      |

| 10  | $REF_IN/REF_OUT$ | Internal +2.5V Reference, External Reference Input |

| 11  | COM              | Common to Analog Input Channel                     |

| 12  | A0               | Slave Address Bit 0                                |

| 13  | A1               | Slave Address Bit 1                                |

| 14  | SCL              | Serial Clock                                       |

| 15  | SDA              | Serial Data                                        |

| 16  | +V <sub>DD</sub> | Power Supply, 3.3V Nominal                         |

## **ELECTRICAL CHARACTERISTICS: +2.7V**

At  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ ,  $+V_{DD} = +2.7\text{V}$ ,  $V_{REF} = +2.5\text{V}$ , SCL Clock Frequency = 3.4MHz (High-Speed Mode), unless otherwise noted.

|                                                                                                                                                                                                   |                                                                                                                                                                                            |                                | ADS7828E                                                 |                                                               |                                |                                                            |                                                               |                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------------------------|---------------------------------------------------------------|--------------------------------|------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------|

| PARAMETER                                                                                                                                                                                         | CONDITIONS                                                                                                                                                                                 | MIN                            | TYP                                                      | MAX                                                           | MIN                            | TYP                                                        | MAX                                                           | UNITS                                                            |

| ANALOG INPUT Full-Scale Input Scan Absolute Input Range Capacitance Leakage Current                                                                                                               | Positive Input - Negative Input<br>Positive Input<br>Negative Input                                                                                                                        | 0<br>-0.2<br>-0.2              | 25<br>±1                                                 | V <sub>REF</sub><br>+V <sub>DD</sub> + 0.2<br>+0.2            | 0<br>-0.2<br>-0.2              | 25<br>±1                                                   | V <sub>REF</sub><br>+V <sub>DD</sub> + 0.2<br>+0.2            | V<br>V<br>V<br>pF<br>μA                                          |

| SYSTEM PERFORMANCE  No Missing Codes Integral Linearity Error Differential Linearity Error Offset Error Offset Error Match Gain Error Gain Error Match Noise Power-Supply Rejection               |                                                                                                                                                                                            | 12                             | ±1.0<br>±1.0<br>±1.0<br>±0.2<br>±1.0<br>±0.2<br>33<br>82 | ±2<br>±3<br>±1<br>±4<br>±1                                    | 12                             | ±0.5<br>±0.5<br>±0.75<br>±0.2<br>±0.75<br>±0.2<br>33<br>82 | ±1<br>-1, +2<br>±2<br>±1<br>±3<br>±1                          | Bits<br>LSB(1)<br>LSB<br>LSB<br>LSB<br>LSB<br>LSB<br>MVRMS<br>dB |

| SAMPLING DYNAMICS Throughput Frequency Conversion Time                                                                                                                                            | High Speed Mode: SCL = 3.4MHz Fast Mode: SCL = 400kHz Standard Mode, SCL = 100kHz                                                                                                          |                                | 6                                                        | 50<br>8<br>2                                                  |                                | 6                                                          | 50<br>8<br>2                                                  | kHz<br>kHz<br>μs                                                 |

| AC ACCURACY Total Harmonic Distortion Signal-to-Ratio Signal-to-(Noise+Distortion) Ratio Spurious-Free Dynamic Range Isolation Channel-to-Channel                                                 | $V_{IN}$ = 2.5 $V_{PP}$ at 10kHz                                                        |                                | -82<br>72<br>71<br>86<br>120                             |                                                               |                                | -82<br>72<br>71<br>86<br>120                               |                                                               | dB <sup>(2)</sup><br>dB<br>dB<br>dB<br>dB                        |

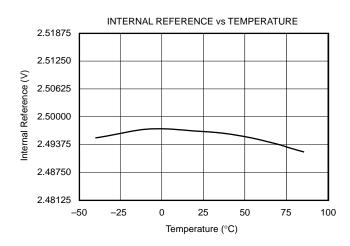

| VOLTAGE REFERENCE OUTPUT Range Internal Reference Drift Output Impedance Quiescent Current                                                                                                        | Internal Reference ON<br>Internal Reference OFF<br>Int. Ref. ON, SCL and SDA pulled HIGH                                                                                                   | 2.475                          | 2.5<br>15<br>110<br>1<br>850                             | 2.525                                                         | 2.475                          | 2.5<br>15<br>110<br>1<br>850                               | 2.525                                                         | V<br>ppm/°C<br>Ω<br>GΩ<br>μΑ                                     |

| VOLTAGE REFERENCE INPUT<br>Range<br>Resistance<br>Current Drain                                                                                                                                   | High Speed Mode: SCL= 3.4MHz                                                                                                                                                               | 0.05                           | 1<br>20                                                  | V <sub>DD</sub>                                               | 0.05                           | 1<br>20                                                    | V <sub>DD</sub>                                               | V<br>GΩ<br>μA                                                    |

| DIGITAL INPUT/OUTPUT Logic Family Logic Levels: V <sub>IH</sub> V <sub>IL</sub> V <sub>OL</sub> Input Leakage: I <sub>IH</sub> I <sub>IL</sub> Data Format                                        | Min. 3mA Sink Current $V_{IH} = +V_{DD} + 0.5$ $V_{IL} = -0.3$                                                                                                                             | +V <sub>DD</sub> • 0.7<br>-0.3 | CMOS Straight Binary                                     | +V <sub>DD</sub> + 0.5<br>+V <sub>DD</sub> • 0.3<br>0.4<br>10 | +V <sub>DD</sub> • 0.7<br>-0.3 | CMOS<br>Straight<br>Binary                                 | +V <sub>DD</sub> + 0.5<br>+V <sub>DD</sub> • 0.3<br>0.4<br>10 | V<br>V<br>V<br>µA<br>µA                                          |

| ADS7828 HARDWARE ADDRESS                                                                                                                                                                          |                                                                                                                                                                                            |                                | 10010                                                    |                                                               |                                | 10010                                                      |                                                               | Binary                                                           |

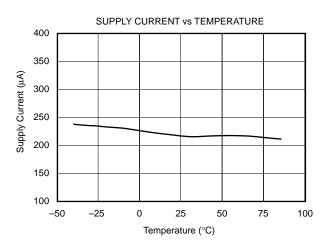

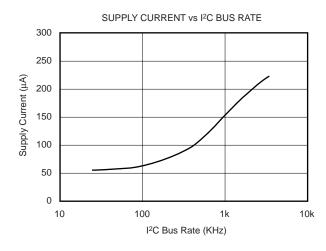

| POWER-SUPPLY REQUIREMENTS Power-Supply Voltage, +V <sub>DD</sub> Quiescent Current  Power Dissipation                                                                                             | Specified Performance High Speed Mode: SCL = 3.4MHz Fast Mode: SCL = 400kHz Standard Mode, SCL = 100kHz High Speed Mode: SCL = 3.4MHz Fast Mode: SCL = 400kHz Standard Modes: SCL = 100kHz | 2.7                            | 225<br>100<br>60<br>675<br>300<br>180                    | 3.6<br>320<br>1000                                            | 2.7                            | 225<br>100<br>60<br>675<br>300<br>180                      | 3.6<br>320<br>1000                                            | V<br>μΑ<br>μΑ<br>μW<br>μW<br>μW                                  |

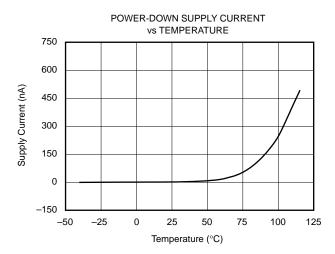

| Power-Down Mode  #/Wrong Address Selected  #/Wrong Address Selected  #/Wrong Address Selected  ### Fast Mode: SCL = 400kHz  ### Standard Mode, SCL = 100kHz  ### SCL Pulled HIGH, SDA Pulled HIGH |                                                                                                                                                                                            |                                | 70<br>25<br>6<br>400                                     | 3000                                                          |                                | 70<br>25<br>6<br>400                                       | 3000                                                          | μΑ<br>μΑ<br>μΑ<br>nA                                             |

| TEMPERATURE RANGE                                                                                                                                                                                 | 1                                                                                                                                                                                          |                                |                                                          | <u> </u>                                                      |                                |                                                            |                                                               |                                                                  |

NOTES: (1) LSB means Least Significant Bit. With  $V_{REF}$  equal to 2.5V, 1LSB is  $610\mu V.$

<sup>(2)</sup> THD measured out to the 9th-harmonic.

## **ELECTRICAL CHARACTERISTICS: +5V**

At  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ ,  $+V_{DD} = +5.0\text{V}$ ,  $V_{REF} = \text{External} +5.0\text{V}$ , SCL Clock Frequency = 3.4MHz (High-Speed Mode), unless otherwise noted.

|                                                                                                                                                                          |                                                                                                                                                                     |                                        | ADS7828E                                |                                                               | 4                                      | ADS7828EB                               |                                                               |                                           |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------|---------------------------------------------------------------|----------------------------------------|-----------------------------------------|---------------------------------------------------------------|-------------------------------------------|--|

| PARAMETER                                                                                                                                                                | CONDITIONS                                                                                                                                                          | MIN                                    | TYP                                     | MAX                                                           | MIN                                    | TYP                                     | MAX                                                           | UNITS                                     |  |

| ANALOG INPUT Full-Scale Input Scan Absolute Input Range Capacitance Leakage Current                                                                                      | Positive Input - Negative Input<br>Positive Input<br>Negative Input                                                                                                 | 0<br>-0.2<br>-0.2                      | 25<br>±1                                | V <sub>REF</sub><br>+V <sub>DD</sub> + 0.2<br>+0.2            | 0<br>-0.2<br>-0.2                      | 25<br>±1                                | V <sub>REF</sub><br>+V <sub>DD</sub> + 0.2<br>+0.2            | V<br>V<br>V<br>pF<br>μA                   |  |

| SYSTEM PERFORMANCE  No Missing Codes Integral Linearity Error Differential Linearity Error Offset Error Offset Error Match Gain Error Match Noise Power-Supply Rejection |                                                                                                                                                                     | 12                                     | ±1.0<br>±1.0<br>±1.0<br>±1.0            | ±2<br>±3<br>±1<br>±3<br>±1                                    | 12                                     | ±0.5<br>±0.5<br>±0.75<br>±0.75<br>±0.75 | ±1<br>-1, +2<br>±2<br>±1<br>±2<br>±1                          | Bits LSB(1) LSB LSB LSB LSB LSB LSB dB    |  |

| SAMPLING DYNAMICS Throughput Frequency Conversion Time                                                                                                                   | High Speed Mode: SCL = 3.4MHz Fast Mode: SCL = 400kHz Standard Mode, SCL = 100kHz                                                                                   |                                        | 6                                       | 50<br>8<br>2                                                  |                                        | 6                                       | 50<br>8<br>2                                                  | kHz<br>kHz<br>kHz<br>μs                   |  |

| AC ACCURACY Total Harmonic Distortion Signal-to-Ratio Signal-to-(Noise+Distortion) Ratio Spurious-Free Dynamic Range Isolation Channel-to-Channel                        | $V_{IN} = 2.5V_{PP}$ at 10kHz                                             |                                        | -82<br>72<br>71<br>86<br>120            |                                                               |                                        | -82<br>72<br>71<br>86<br>120            |                                                               | dB <sup>(2)</sup><br>dB<br>dB<br>dB<br>dB |  |

| VOLTAGE REFERENCE OUTPUT Range Internal Reference Drift Output Impedance Quiescent Current                                                                               | Internal Reference ON<br>Internal Reference OFF<br>Int. Ref. ON, SCL and SDA pulled HIGH                                                                            | 2.475                                  | 2.5<br>15<br>110<br>1<br>1300           | 2.525                                                         | 2.475                                  | 2.5<br>15<br>110<br>1<br>1300           | 2.525                                                         | V<br>ppm/°C<br>Ω<br>GΩ<br>μΑ              |  |

| VOLTAGE REFERENCE INPUT<br>Range<br>Resistance<br>Current Drain                                                                                                          | High Speed Mode: SCL = 3.4MHz                                                                                                                                       | 0.05                                   | 1<br>20                                 | V <sub>DD</sub>                                               | 0.05                                   | 1<br>20                                 | V <sub>DD</sub>                                               | V<br>GΩ<br>μA                             |  |

| DIGITAL INPUT/OUTPUT Logic Family Logic Levels: V <sub>IH</sub> V <sub>IL</sub> V <sub>OL</sub> Input Leakage: I <sub>IH</sub> I <sub>IL</sub> Data Format               | Min. 3mA Sink Current $V_{IH} = +V_{DD} +0.5$ $V_{IL} = -0.3$                                                                                                       | CMOS<br>+V <sub>DD</sub> • 0.7<br>-0.3 | Straight<br>Binary                      | +V <sub>DD</sub> + 0.5<br>+V <sub>DD</sub> • 0.3<br>0.4<br>10 | CMOS<br>+V <sub>DD</sub> • 0.7<br>-0.3 | Straight<br>Binary                      | +V <sub>DD</sub> + 0.5<br>+V <sub>DD</sub> • 0.3<br>0.4<br>10 | V<br>V<br>V<br>μΑ<br>μΑ                   |  |

| ADS7828 HARDWARE ADDRESS                                                                                                                                                 |                                                                                                                                                                     |                                        | 10010                                   |                                                               |                                        | 10010                                   |                                                               | Binary                                    |  |

| POWER-SUPPLY REQUIREMENTS Power-Supply Voltage, +V <sub>DD</sub> Quiescent Current                                                                                       | Specified Performance High Speed Mode: SCL = 3.4MHz Fast Mode: SCL = 400kHz Standard Mode, SCL = 100kHz                                                             | 4.75                                   | 5<br>750<br>300<br>150                  | 5.25<br>1000                                                  | 4.75                                   | 5<br>750<br>300<br>150                  | 5.25<br>1000                                                  | V<br>μΑ<br>μΑ<br>μΑ                       |  |

| Power Dissipation  Power-Down Mode  w/Wrong Address Selected                                                                                                             | High Speed Mode: SCL = 3.4MHz Fast Mode: SCL = 400kHz Standard Mode, SCL = 100kHz High Speed Mode: SCL = 3.4MHz Fast Mode: SCL = 400kHz Standard Mode, SCL = 100kHz |                                        | 3.75<br>1.5<br>0.75<br>400<br>150<br>35 | 5                                                             |                                        | 3.75<br>1.5<br>0.75<br>400<br>150<br>35 | 5                                                             | mW<br>mW<br>mW<br>μA<br>μA<br>μA          |  |

| Full Power-Down TEMPERATURE RANGE                                                                                                                                        | SCL Pulled HIGH, SDA Pulled HIGH                                                                                                                                    |                                        | 400                                     | 3000                                                          |                                        | 400                                     | 3000                                                          | nA                                        |  |

NOTES: (1) LSB means Least Significant Bit. With  $V_{REF}$  equal to 5.0V, 1LSB is 1.22mV.

<sup>(2)</sup> THD measured out to the 9th-harmonic.

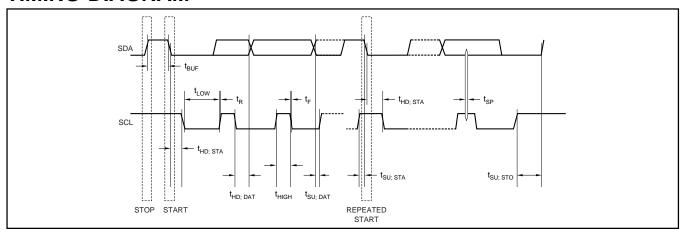

## **TIMING DIAGRAM**

## TIMING CHARACTERISTICS(1)

At  $T_A = -40^{\circ}C$  to +85°C, +V<sub>DD</sub> = +2.7V, unless otherwise noted.

| PARAMETER                                                                                   | SYMBOL                           | CONDITIONS                                                                                                           | MIN                                            | MAX                      | UNITS                    |

|---------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------|--------------------------|

| SCL Clock Frequency                                                                         | f <sub>SCL</sub>                 | Standard Mode<br>Fast Mode<br>High-Speed Mode, $C_B = 100 pF$ max<br>High-Speed Mode, $C_B = 400 pF$ max             |                                                | 100<br>400<br>3.4<br>1.7 | kHz<br>kHz<br>MHz<br>MHz |

| Bus Free Time Between a STOP and START Condition                                            | t <sub>BUF</sub>                 | Standard Mode<br>Fast Mode                                                                                           | 4.7<br>1.3                                     |                          | μs<br>μs                 |

| Hold Time (Repeated) START<br>Condition                                                     | t <sub>HD</sub> ; <sub>STA</sub> | Standard Mode<br>Fast Mode<br>High-Speed Mode                                                                        | 4.0<br>600<br>160                              |                          | μs<br>ns<br>ns           |

| LOW Period of the SCL Clock                                                                 | t <sub>LOW</sub>                 | Standard Mode<br>Fast Mode<br>High-Speed Mode, $C_B = 100 pF max^{(2)}$<br>High-Speed Mode, $C_B = 400 pF max^{(2)}$ | 4.7<br>1.3<br>160<br>320                       |                          | μs<br>μs<br>ns<br>ns     |

| HIGH Period of the SCL Clock                                                                | t <sub>HIGH</sub>                | Standard Mode<br>Fast Mode<br>High-Speed Mode, $C_B = 100 pF max^{(2)}$<br>High-Speed Mode, $C_B = 400 pF max^{(2)}$ | 4.0<br>600<br>60<br>120                        |                          | μs<br>ns<br>ns<br>ns     |

| Setup Time for a Repeated START Condition                                                   | t <sub>SU</sub> ; <sub>STA</sub> | Standard Mode<br>Fast Mode<br>High-Speed Mode                                                                        | 4.7<br>600<br>160                              |                          | μs<br>ns<br>ns           |

| Data Setup Time                                                                             | t <sub>SU</sub> ; <sub>DAT</sub> | Standard Mode<br>Fast Mode<br>High-Speed Mode                                                                        | 250<br>100<br>10                               |                          | ns<br>ns<br>ns           |

| Data Hold Time                                                                              | t <sub>HD</sub> ; <sub>DAT</sub> | Standard Mode<br>Fast Mode<br>High-Speed Mode, $C_B = 100 pF max^{(2)}$<br>High-Speed Mode, $C_B = 400 pF max^{(2)}$ | 0<br>0<br>0 <sup>(3)</sup><br>0 <sup>(3)</sup> | 3.45<br>0.9<br>70<br>150 | μs<br>μs<br>ns<br>ns     |

| Rise Time of SCL Signal                                                                     | t <sub>RCL</sub>                 | Standard Mode<br>Fast Mode<br>High-Speed Mode, $C_B = 100 pF max^{(2)}$<br>High-Speed Mode, $C_B = 400 pF max^{(2)}$ | 20 + 0.1C <sub>B</sub><br>10<br>20             | 1000<br>300<br>40<br>80  | ns<br>ns<br>ns<br>ns     |

| Rise Time of SCL Signal After a<br>Repeated START Condition and<br>After an Acknowledge Bit | t <sub>RCL1</sub>                | Standard Mode<br>Fast Mode<br>High-Speed Mode, $C_B = 100 pF max^{(2)}$<br>High-Speed Mode, $C_B = 400 pF max^{(2)}$ | 20 + 0.1C <sub>B</sub><br>10<br>20             | 1000<br>300<br>80<br>160 | ns<br>ns<br>ns<br>ns     |

| Fall Time of SCL Signal $t_{FCL}$                                                           |                                  | Standard Mode<br>Fast Mode<br>High-Speed Mode, $C_B = 100pF max^{(2)}$<br>High-Speed Mode, $C_B = 400pF max^{(2)}$   | 20 + 0.1C <sub>B</sub><br>10<br>20             | 300<br>300<br>40<br>80   | ns<br>ns<br>ns           |

NOTES: (1) All values referred to  $V_{\text{IHMIN}}$  and  $V_{\text{ILMAX}}$  levels.

<sup>(2)</sup> For bus line loads  $C_B$  between 100pF and 400pF the timing parameters must be linearly interpolated.

<sup>(3)</sup> A device must internally provide a data hold time to bridge the undefined part between V<sub>IH</sub> and V<sub>IL</sub> of the falling edge of the SCLH signal. An input circuit with a threshold as low as possible for the falling edge of the SCLH signal minimizes this hold time.

## TIMING CHARACTERISTICS(1) (Cont.)

At  $T_A = -40$ °C to +85°C, +V<sub>DD</sub> = +2.7V, unless otherwise noted.

| PARAMETER                                                                            | SYMBOL                | CONDITIONS                                                 | MIN                    | MAX  | UNITS |

|--------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------|------------------------|------|-------|

| Rise Time of SDA Signal                                                              | t <sub>RDA</sub>      | Standard Mode                                              |                        | 1000 | ns    |

|                                                                                      |                       | Fast Mode                                                  | 20 + 0.1C <sub>B</sub> | 300  | ns    |

|                                                                                      |                       | High-Speed Mode, C <sub>B</sub> = 100pF max <sup>(2)</sup> | 10                     | 80   | ns    |

|                                                                                      |                       | High-Speed Mode, $C_B = 400pF max^{(2)}$                   | 20                     | 160  | ns    |

| Fall Time of SDA Signal                                                              | t <sub>FDA</sub>      | Standard Mode                                              |                        | 300  | ns    |

|                                                                                      |                       | Fast Mode                                                  | 20 + 0.1C <sub>B</sub> | 300  | ns    |

|                                                                                      |                       | High-Speed Mode, C <sub>B</sub> = 100pF max <sup>(2)</sup> | 10                     | 80   | ns    |

|                                                                                      |                       | High-Speed Mode, $C_B = 400pF max^{(2)}$                   | 20                     | 160  | ns    |

| Setup Time for STOP Condition                                                        | t <sub>su</sub> ; sто | Standard Mode                                              | 4.0                    |      | μѕ    |

| •                                                                                    |                       | Fast Mode                                                  | 600                    |      | ns    |

|                                                                                      |                       | High-Speed Mode                                            | 160                    |      | ns    |

| Capacitive Load for SDA and SCL Line                                                 | Св                    |                                                            |                        | 400  | pF    |

| Pulse Width of Spike Suppressed                                                      | t <sub>SP</sub>       | Fast Mode                                                  |                        | 50   | ns    |

|                                                                                      | GI GI                 | High-Speed Mode                                            |                        | 10   | ns    |

| Noise Margin at the HIGH Level for Each Connected Device (Including Hysteresis)      | $V_{NH}$              | Standard Mode<br>Fast Mode<br>High-Speed Mode              | 0.2V <sub>DD</sub>     |      | V     |

| Noise Margin at the LOW Level for<br>Each Connected Device (Including<br>Hysteresis) | V <sub>NL</sub>       | Standard Mode<br>Fast Mode<br>High-Speed Mode              | 0.1V <sub>DD</sub>     |      | V     |

NOTES: (1) All values referred to  $V_{\text{IHMIN}}$  and  $V_{\text{ILMAX}}$  levels.

<sup>(2)</sup> For bus line loads C<sub>B</sub> between 100pF and 400pF the timing parameters must be linearly interpolated.

(3) A device must internally provide a data hold time to bridge the undefined part between V<sub>IH</sub> and V<sub>IL</sub> of the falling edge of the SCLH signal. An input circuit with a threshold as low as possible for the falling edge of the SCLH signal minimizes this hold time.

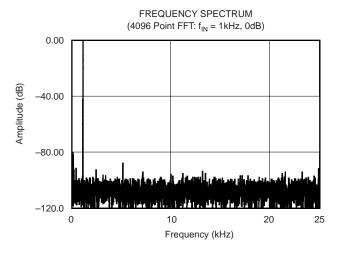

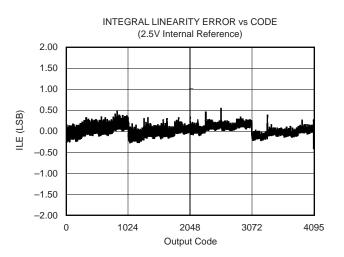

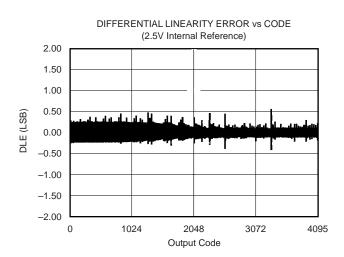

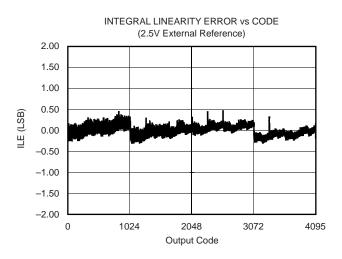

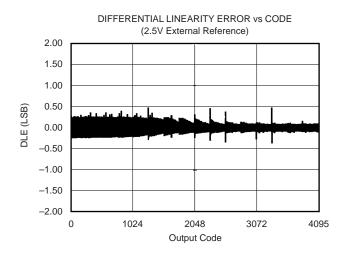

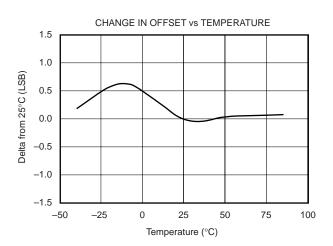

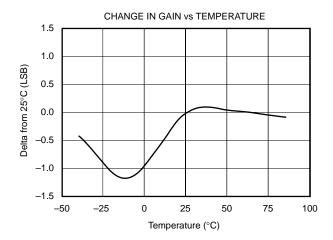

## TYPICAL CHARACTERISTICS

$T_A$  = +25°C,  $V_{DD}$  = +2.7V,  $V_{REF}$  = External +2.5V,  $f_{SAMPLE}$  = 50kHz, unless otherwise noted.

## **TYPICAL CHARACTERISTICS (Cont.)**

$T_{A} = +25^{\circ}C, \ V_{DD} = +2.7V, \ V_{REF} = \text{External } +2.5V, \ f_{SAMPLE} = 50 \text{kHz}, \ unless \ otherwise \ noted.$

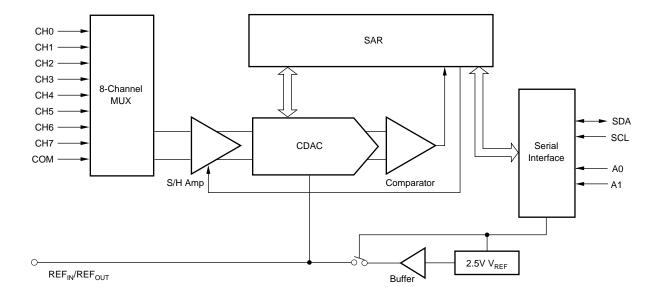

#### THEORY OF OPERATION

The ADS7828 is a classic Successive Approximation Register (SAR) A/D converter. The architecture is based on capacitive redistribution which inherently includes a sample-and-hold function. The converter is fabricated on a  $0.6\mu$  CMOS process.

The ADS7828 core is controlled by an internally generated free-running clock. When the ADS7828 is not performing conversions or being addressed, it keeps the A/D converter core powered off, and the internal clock does not operate.

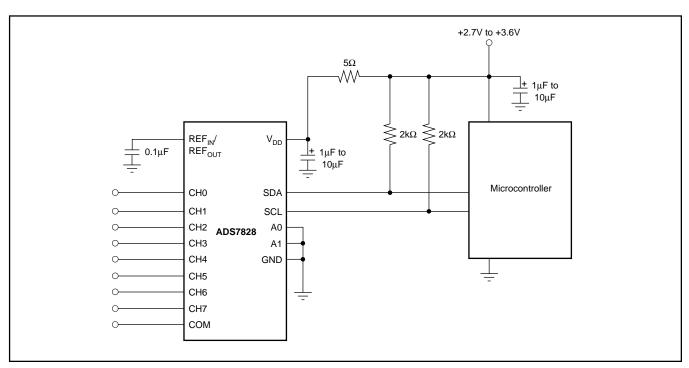

The simplified diagram of input and output for the ADS7828 is shown in Figure 1.

#### **ANALOG INPUT**

When the converter enters the hold mode, the voltage on the selected CHx pin is captured on the internal capacitor array. The input current on the analog inputs depends on the conversion rate of the device. During the sample period, the source must charge the internal sampling capacitor (typically 25pF). After the capacitor has been fully charged, there is no further input current. The amount of charge transfer from the analog source to the converter is a function of conversion rate.

#### **REFERENCE**

The ADS7828 can operate with an internal 2.5V reference or an external reference. If a +5V supply is used, an external +5V reference is required in order to provide full dynamic range for a 0V to  $+V_{DD}$  analog input. This external reference can be as low as 50mV. When using a +2.7V supply, the

internal +2.5V reference will provide full dynamic range for a 0V to +V<sub>DD</sub> analog input.

As the reference voltage is reduced, the analog voltage weight of each digital output code is reduced. This is often referred to as the LSB (least significant bit) size and is equal to the reference voltage divided by 4096. This means that any offset or gain error inherent in the A/D converter will appear to increase, in terms of LSB size, as the reference voltage is reduced.

The noise inherent in the converter will also appear to increase with lower LSB size. With a 2.5V reference, the internal noise of the converter typically contributes only 0.32LSB peak-to-peak of potential error to the output code. When the external reference is 50mV, the potential error contribution from the internal noise will be 50 times larger—16LSBs. The errors due to the internal noise are Gaussian in nature and can be reduced by averaging consecutive conversion results.

#### **DIGITAL INTERFACE**

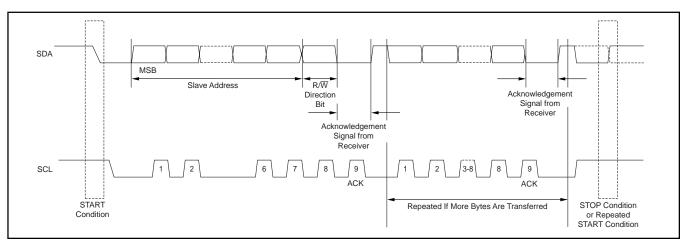

The ADS7828 supports the I<sup>2</sup>C serial bus and data transmission protocol, in all three defined modes: standard, fast, and high-speed. A device that sends data onto the bus is defined as a transmitter, and a device receiving data as a receiver. The device that controls the message is called a "master." The devices that are controlled by the master are "slaves." The bus must be controlled by a master device that generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions. The ADS7828 operates as a slave on the I<sup>2</sup>C bus. Connections to the bus are made via the open-drain I/O lines SDA and SCL.

FIGURE 1. Simplified I/O of the ADS7828.

The following bus protocol has been defined (as shown in Figure 2):

- Data transfer may be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as control signals.

Accordingly, the following bus conditions have been defined:

Bus Not Busy: Both data and clock lines remain HIGH.

**Start Data Transfer:** A change in the state of the data line, from HIGH to LOW, while the clock is HIGH, defines a START condition.

**Stop Data Transfer:** A change in the state of the data line, from LOW to HIGH, while the clock line is HIGH, defines the STOP condition.

**Data Valid:** The state of the data line represents valid data, when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal. There is one clock pulse per bit of data.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of data bytes transferred between START and STOP conditions is not limited and is determined by the master device. The information is transferred byte-wise and each receiver acknowledges with a ninth-bit.

Within the I<sup>2</sup>C bus specifications a standard mode (100kHz clock rate), a fast mode (400kHz clock rate), and a high-speed mode (3.4MHz clock rate) are defined. The ADS7828 works in all three modes.

**Acknowledge:** Each receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse that is associated with this acknowledge bit.

A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge clock pulse. Of course, setup and hold times

must be taken into account. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition.

Figure 2 details how data transfer is accomplished on the  $I^2C$  bus. Depending upon the state of the  $R/\overline{W}$  bit, two types of data transfer are possible:

- Data transfer from a master transmitter to a slave receiver. The first byte transmitted by the master is the slave address. Next follows a number of data bytes. The slave returns an acknowledge bit after the slave address and each received byte.

- 2. Data transfer from a slave transmitter to a master receiver. The first byte, the slave address, is transmitted by the master. The slave then returns an acknowledge bit. Next, a number of data bytes are transmitted by the slave to the master. The master returns an acknowledge bit after all received bytes other than the last byte. At the end of the last received byte, a not-acknowledge is returned.

The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or a repeated START condition. Since a repeated START condition is also the beginning of the next serial transfer, the bus will not be released.

The ADS7828 may operate in the following two modes:

- Slave Receiver Mode: Serial data and clock are received through SDA and SCL. After each byte is received, an acknowledge bit is transmitted. START and STOP conditions are recognized as the beginning and end of a serial transfer. Address recognition is performed by hardware after reception of the slave address and direction bit.

- Slave Transmitter Mode: The first byte (the slave address) is received and handled as in the slave receiver mode. However, in this mode the direction bit will indicate that the transfer direction is reversed. Serial data is transmitted on SDA by the ADS7828 while the serial clock is input on SCL. START and STOP conditions are recognized as the beginning and end of a serial transfer.

FIGURE 2. Basic Operation of the ADS7828.

#### **ADDRESS BYTE**

| MSB | 6 | 5 | 4 | 3 | 2  | 1  | LSB |

|-----|---|---|---|---|----|----|-----|

| 1   | 0 | 0 | 1 | 0 | A1 | A0 | R/W |

The address byte is the first byte received following the START condition from the master device. The first five bits (MSBs) of the slave address are factory pre-set to 10010. The next two bits of the address byte are the device select bits, A1 and A0. Input pins (A1-A0) on the ADS7828 determine these two bits of the device address for a particular ADS7828. A maximum of four devices with the same pre-set code can therefore be connected on the same bus at one time.

The A1-A0 Address Inputs can be connected to  $V_{DD}$  or digital ground. The device address is set by the state of these pins upon power-up of the ADS7828.

The last bit of the address byte  $(R\overline{\mathcal{M}})$  defines the operation to be performed. When set to a '1' a read operation is selected; when set to a '0' a write operation is selected. Following the START condition the ADS7828 monitors the SDA bus, checking the device type identifier being transmitted. Upon receiving the 10010 code, the appropriate device select bits, and the  $R\overline{\mathcal{M}}$  bit, the slave device outputs an acknowledge signal on the SDA line.

#### **COMMAND BYTE**

| MSB | 6  | 5  | 4  | 3   | 2   | 1 | LSB |

|-----|----|----|----|-----|-----|---|-----|

| SD  | C2 | C1 | C0 | PD1 | PD0 | Х | Х   |

The ADS7828 operating mode is determined by a command byte which is illustrated above.

SD: Single-Ended/Differential Inputs

0: Differential Inputs

1: Single-Ended Inputs

C2 - C0: Channel Selections

PD1 - 0: Power-Down Selection

X: Unused

See Table I for a power-down selection summary.

See Table II for a channel selection control summary.

| PD1 | PD0 | DESCRIPTION                                  |

|-----|-----|----------------------------------------------|

| 0   | 0   | Power Down Between A/D Converter Conversions |

| 0   | 1   | Internal Reference OFF and A/D Converter ON  |

| 1   | 0   | Internal Reference ON and A/D Converter OFF  |

| 1   | 1   | Internal Reference ON and A/D Converter ON   |

TABLE I. Power-Down Selection

|    |    |    |    |     | CHANNEL | SELECTIO | N CONTRO | L   |     |     |     |     |

|----|----|----|----|-----|---------|----------|----------|-----|-----|-----|-----|-----|

| SD | C2 | C1 | C0 | CH0 | CH1     | CH2      | СНЗ      | CH4 | CH5 | CH6 | CH7 | СОМ |

| 0  | 0  | 0  | 0  | +IN | -IN     | _        | _        | _   | _   | _   | _   | -   |

| 0  | 0  | 0  | 1  | _   | _       | +IN      | -IN      | _   | _   | _   | _   | _   |

| 0  | 0  | 1  | 0  | _   | _       | _        | _        | +IN | -IN | _   | _   | _   |

| 0  | 0  | 1  | 1  | _   | _       | _        | _        | _   | _   | +IN | -IN | -   |

| 0  | 1  | 0  | 0  | -IN | +IN     | _        | _        | _   |     | 1   | _   | 1   |

| 0  | 1  | 0  | 1  | _   | _       | -IN      | +IN      | _   | -   |     | _   | ı   |

| 0  | 1  | 1  | 0  | _   | _       | _        | _        | -IN | +IN |     | _   | ı   |

| 0  | 1  | 1  | 1  | _   | _       | _        | _        | _   | _   | -IN | +IN | 1   |

| 1  | 0  | 0  | 0  | +IN | _       |          | _        | _   | 1   | ı   | _   | -IN |

| 1  | 0  | 0  | 1  | _   | _       | +IN      | _        | _   | -   |     | _   | -IN |

| 1  | 0  | 1  | 0  | _   | _       | _        | _        | +IN | -   |     | _   | -IN |

| 1  | 0  | 1  | 1  | _   | _       | _        | _        | _   | _   | +IN | _   | -IN |

| 1  | 1  | 0  | 0  | _   | +IN     | _        | _        | _   |     | -   | _   | -IN |

| 1  | 1  | 0  | 1  | _   | _       | _        | +IN      | _   | _   | _   | _   | -IN |

| 1  | 1  | 1  | 0  | _   | _       | _        | _        | _   | +IN | _   | _   | -IN |

| 1  | 1  | 1  | 1  | _   | _       |          | _        | _   |     |     | +IN | -IN |

TABLE II. Channel Selection Control Addressed by Command Byte.

#### **INITIATING CONVERSION**

Provided the master has write-addressed it, the ADS7828 turns on the A/D converter's section and begins conversions when it receives BIT 4 of the command byte shown in the Command Byte. If the command byte is correct, the ADS7828 will return an ACK condition.

#### **READING DATA**

Data can be read from the ADS7828 by read-addressing the part (LSB of address byte set to 1) and receiving the transmitted bytes. Converted data can only be read from the ADS7828 once a conversion has been initiated as described in the preceding section.

Each 12-bit data word is returned in two bytes, as shown below, where D11 is the MSB of the data word, and D0 is the LSB. Byte 0 is sent first, followed by Byte 1.

|        | MSB | 6  | 5  | 4  | 3   | 2   | 1  | LSB |

|--------|-----|----|----|----|-----|-----|----|-----|

| BYTE 0 | 0   | 0  | 0  | 0  | D11 | D10 | D9 | D8  |

| BYTE 1 | D7  | D6 | D5 | D4 | D3  | D2  | D1 | D0  |

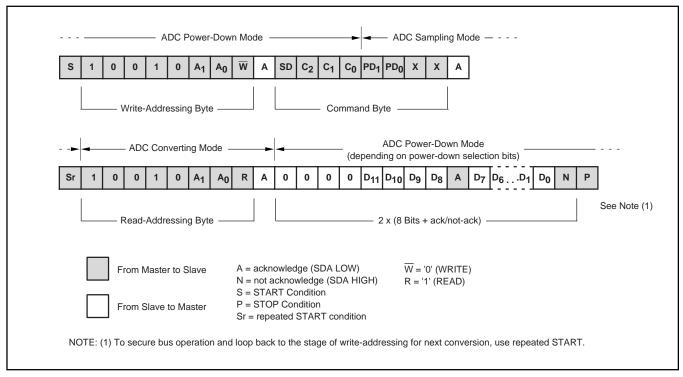

#### **READING IN F/S MODE**

Figure 3 describes the interaction between the master and the slave ADS7828 in Fast or Standard (F/S) mode. At the end of reading conversion data the ADS7828 can be issued a repeated START condition by the master to secure bus operation for subsequent conversions of the A/D converter. This would be the most efficient way to perform continuous conversions.

FIGURE 3. Typical Read Sequence in F/S Mode.

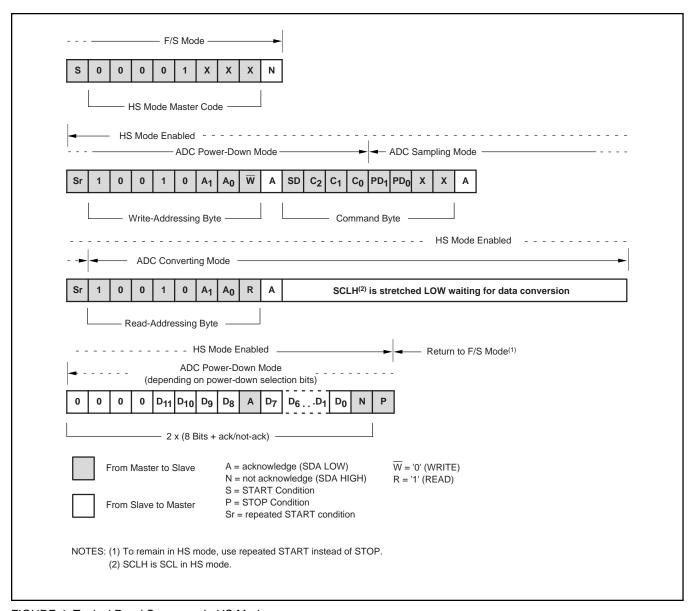

#### **READING IN HS MODE**

High Speed (HS) mode is fast enough that codes can be read out one at a time. In HS mode, there is not enough time for a single conversion to complete between the reception of a repeated START condition and the read-addressing byte, so the ADS7828 stretches the clock after the read-addressing byte has been fully received, holding it LOW until the conversion is complete.

See Figure 4 for a typical read sequence for HS mode. Included in the read sequence is the shift from F/S to HS modes. It may be desirable to remain in HS mode after reading a conversion; to do this, issue a repeated START instead of a STOP at the end of the read sequence, since a STOP causes the part to return to F/S mode.

FIGURE 4. Typical Read Sequence in HS Mode.

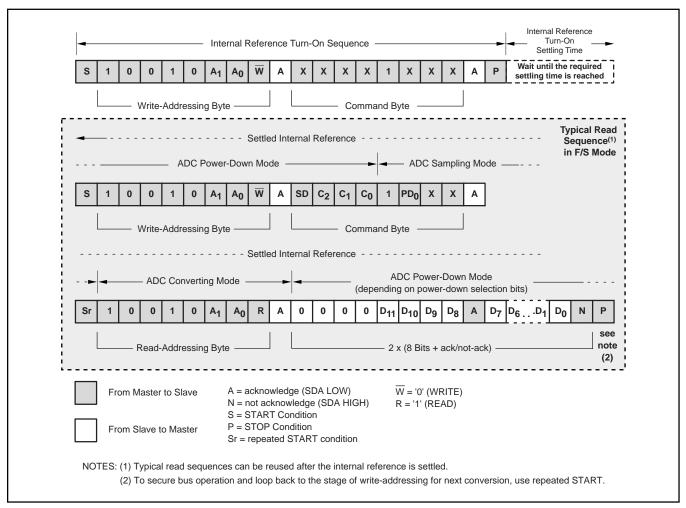

#### READING WITH REFERENCE ON/OFF

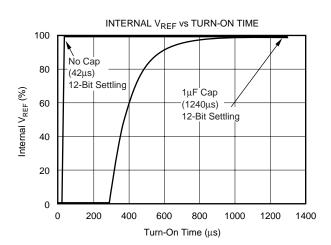

The internal reference defaults to off when the ADS7828 power is on. To turn the internal reference on or off, see Table I. If the reference (internal or external) is constantly turned on and off, a proper amount of settling time must be added before a normal conversion cycle can be started. The exact amount of settling time needed varies depending on the configuration.

See Figure 5 for an example of the proper internal reference turn-on sequence before issuing the typical read sequences required for the F/S mode when an internal reference is used.

When using an internal reference, there are three things that must be done:

- In order to use the internal reference, the PD1 bit of Command Byte must always be set to logic '1' for each sample conversion that is issued by the sequence, as shown in Figure 3.

- 2) In order to achieve 12-bit accuracy conversion when using the internal reference, the internal reference settling time must be considered, as shown in the

Internal  $V_{REF}$  vs Turn-On Time Typical Characteristic plot. If the PD1 bit has been set to logic '0' while using the ADS7828, then the settling time must be reconsidered after PD1 is set to logic '1'. In other words, whenever the internal reference is turned on after it has been turned off, the settling time must be long enough to get 12-bit accuracy conversion.

3) When the internal reference is off, it is not turned on until both the first Command Byte with PD1 = '1' is sent and then a STOP condition or repeated START condition is issued. (The actual turn-on time occurs once the STOP or repeated START condition is issued.) Any Command Byte with PD1 = '1' issued after the internal reference is turned on serves only to keep the internal reference on. Otherwise, the internal reference would be turned off by any Command Byte with PD1 = '0'.

The example in Figure 5 can be generalized for a HS mode conversion cycle by simply swapping the timing of the conversion cycle.

If using an external reference, PD1 must be set to '0', and the external reference must be settled. The typical sequence in Figure 3 or Figure 4 can then be used.

FIGURE 5. Internal Reference Turn-On Sequence and Typical Read Sequence (F/S mode shown).

#### **LAYOUT**

For optimum performance, care should be taken with the physical layout of the ADS7828 circuitry. The basic SAR architecture is sensitive to glitches or sudden changes on the power supply, reference, ground connections, and digital inputs that occur just prior to latching the output of the analog comparator. Therefore, during any single conversion for an "n-bit" SAR converter, there are n "windows" in which large external transient voltages can easily affect the conversion result. Such glitches might originate from switching power supplies, nearby digital logic, and high-power devices.

With this in mind, power to the ADS7828 should be clean and well-bypassed. A  $0.1\mu F$  ceramic bypass capacitor should be placed as close to the device as possible. A  $1\mu F$  to  $10\mu F$  capacitor may also be needed if the impedance of the connection between +V<sub>DD</sub> and the power supply is high.

The ADS7828 architecture offers no inherent rejection of noise or voltage variation in regards to using an external reference input. This is of particular concern when the reference input is tied to the power supply. Any noise and ripple from the supply will appear directly in the digital results. While high-frequency noise can be filtered out, voltage variation due to line frequency (50Hz or 60Hz) can be difficult to remove.

The GND pin should be connected to a clean ground point. In many cases, this will be the "analog" ground. Avoid connections that are too near the grounding point of a microcontroller or digital signal processor. The ideal layout will include an analog ground plane dedicated to the converter and associated analog circuitry.

www.ti.com 16-Aug-2023

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|----------------------|---------|

| ADS7828E/250     | ACTIVE | TSSOP        | PW                 | 16   | 250            | RoHS & Green | (6)<br>Call TI                | Level-1-260C-UNLIM | -40 to 85    | ADS<br>7828E         | Samples |

| ADS7828E/250G4   | ACTIVE | TSSOP        | PW                 | 16   | 250            | RoHS & Green | Call TI                       | Level-1-260C-UNLIM | -40 to 85    | ADS<br>7828E         | Samples |

| ADS7828E/2K5     | ACTIVE | TSSOP        | PW                 | 16   | 2500           | RoHS & Green | Call TI                       | Level-1-260C-UNLIM | -40 to 85    | ADS<br>7828E         | Samples |

| ADS7828E/2K5G4   | ACTIVE | TSSOP        | PW                 | 16   | 2500           | RoHS & Green | Call TI                       | Level-1-260C-UNLIM | -40 to 85    | ADS<br>7828E         | Samples |

| ADS7828EB/250    | ACTIVE | TSSOP        | PW                 | 16   | 250            | RoHS & Green | Call TI                       | Level-1-260C-UNLIM | -40 to 85    | ADS<br>7828E         | Samples |

| ADS7828EB/250G4  | ACTIVE | TSSOP        | PW                 | 16   | 250            | RoHS & Green | Call TI                       | Level-1-260C-UNLIM | -40 to 85    | ADS<br>7828E         | Samples |

| ADS7828EB/2K5    | ACTIVE | TSSOP        | PW                 | 16   | 2500           | RoHS & Green | Call TI                       | Level-1-260C-UNLIM | -40 to 85    | ADS<br>7828E         | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

(3) MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

(4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

### **PACKAGE OPTION ADDENDUM**

www.ti.com 16-Aug-2023

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF ADS7828:

Automotive : ADS7828-Q1

NOTE: Qualified Version Definitions:

Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

www.ti.com 16-Feb-2022

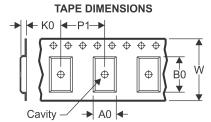

#### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

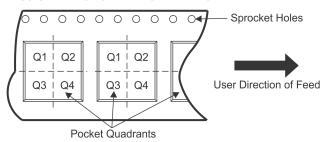

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| All differsions are norminal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|------------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| ADS7828E/250                 | TSSOP           | PW                 | 16 | 250  | 180.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| ADS7828E/2K5                 | TSSOP           | PW                 | 16 | 2500 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| ADS7828EB/250                | TSSOP           | PW                 | 16 | 250  | 180.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| ADS7828EB/2K5                | TSSOP           | PW                 | 16 | 2500 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

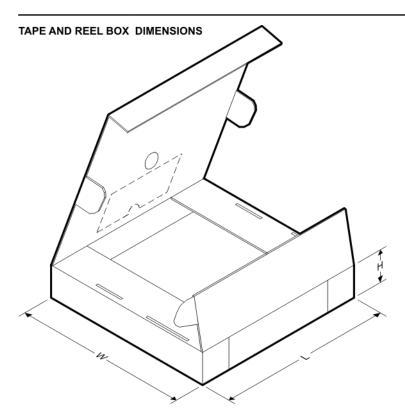

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 16-Feb-2022

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| ADS7828E/250  | TSSOP        | PW              | 16   | 250  | 210.0       | 185.0      | 35.0        |

| ADS7828E/2K5  | TSSOP        | PW              | 16   | 2500 | 367.0       | 367.0      | 35.0        |

| ADS7828EB/250 | TSSOP        | PW              | 16   | 250  | 210.0       | 185.0      | 35.0        |

| ADS7828EB/2K5 | TSSOP        | PW              | 16   | 2500 | 367.0       | 367.0      | 35.0        |

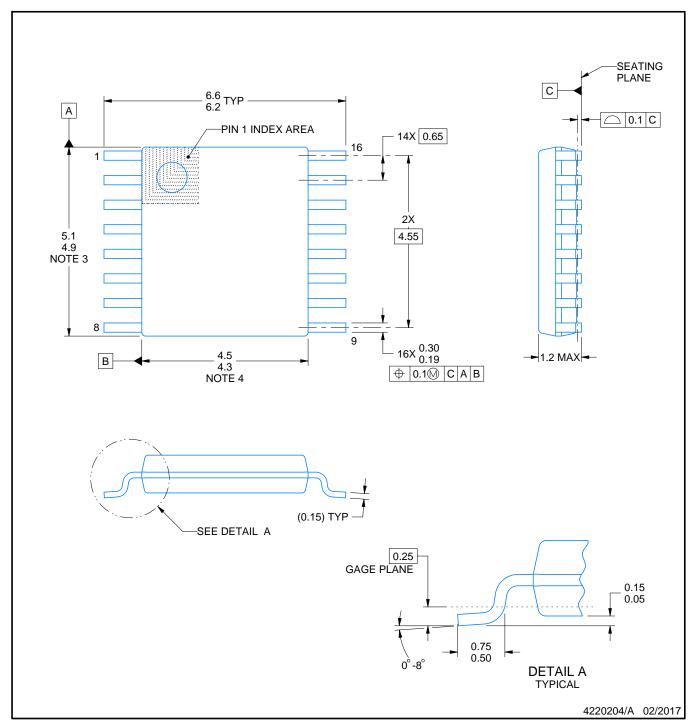

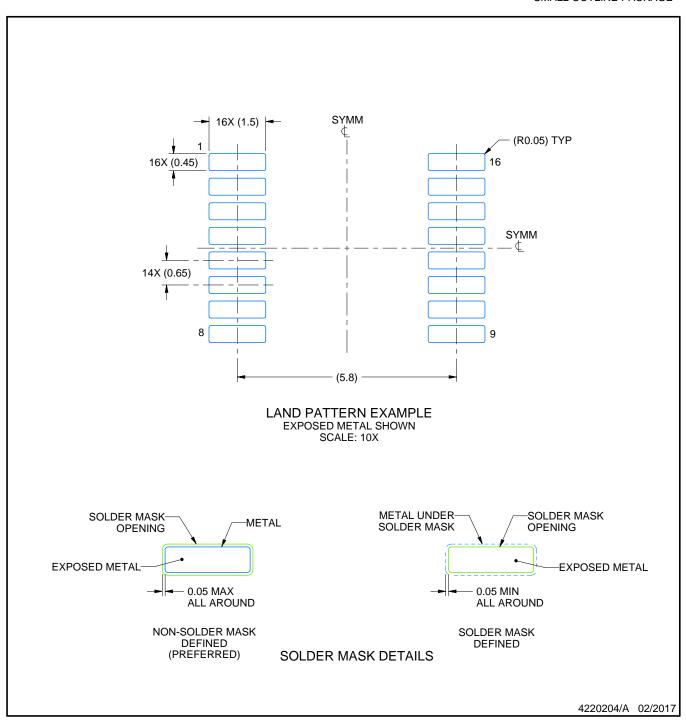

SMALL OUTLINE PACKAGE

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153.

SMALL OUTLINE PACKAGE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

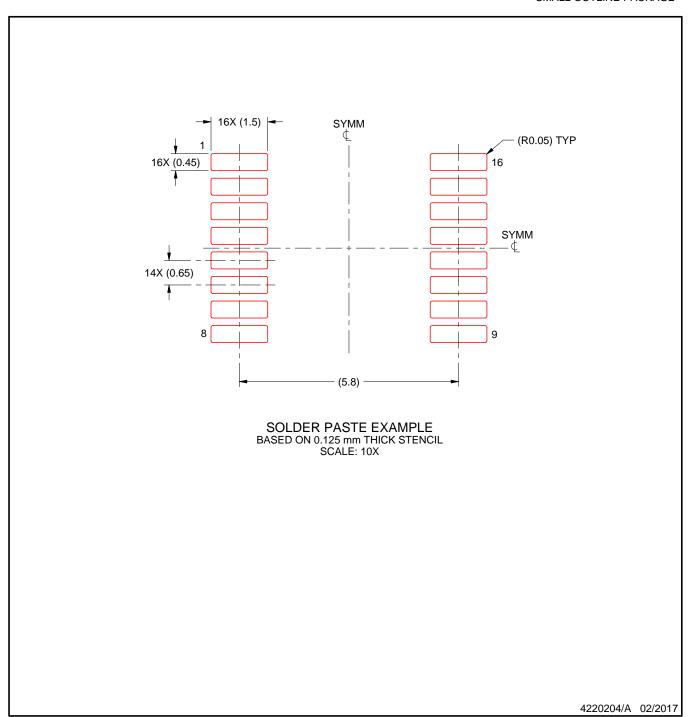

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

#### **IMPORTANT NOTICE AND DISCLAIMER**

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated