# ESP32 Series Datasheet

## Including:

ESP32-D0WD-V3

ESP32-D0WDQ6-V3

ESP32-D0WD

ESP32-D0WDQ6

ESP32-D2WD

ESP32-SOWD

ESP32-U4WDH

Version 3.5 Espressif Systems Copyright © 2021

### **About This Guide**

This document provides the specifications of ESP32 family of chips.

### **Document Updates**

Please always refer to the latest version on <a href="https://www.espressif.com/en/support/download/documents">https://www.espressif.com/en/support/download/documents</a>.

### **Revision History**

For any changes to this document over time, please refer to the last page.

### **Documentation Change Notification**

Espressif provides email notifications to keep customers updated on changes to technical documentation. Please subscribe at <u>www.espressif.com/en/subscribe</u>. Note that you need to update your subscription to receive notifications of new products you are not currently subscribed to.

### Certification

Download certificates for Espressif products from <u>www.espressif.com/en/certificates</u>.

## Contents

| 1   | Ove     | erview                         | 8  |

|-----|---------|--------------------------------|----|

| 1.1 | Featur  | red Solutions                  | 8  |

|     | 1.1.1   | Ultra-Low-Power Solution       | 8  |

|     | 1.1.2   | Complete Integration Solution  | 8  |

| 1.2 | Wi-Fi I | Key Features                   | 8  |

| 1.3 | BT Ke   | ey Features                    | 9  |

| 1.4 | MCU a   | and Advanced Features          | 9  |

|     | 1.4.1   | CPU and Memory                 | 9  |

|     | 1.4.2   | Clocks and Timers              | 10 |

|     | 1.4.3   | Advanced Peripheral Interfaces | 10 |

|     | 1.4.4   | Security                       | 10 |

| 1.5 | Applic  | ations (A Non-exhaustive List) | 11 |

| 1.6 | Block   | Diagram                        | 12 |

| 2   | Pin     | Definitions                    | 13 |

| 2.1 | Pin La  | iyout                          | 13 |

| 2.2 | Pin De  | escription                     | 15 |

| 2.3 | Power   | r Scheme                       | 18 |

| 2.4 | Strapp  | bing Pins                      | 19 |

| 3   | Fur     | nctional Description           | 22 |

| 3.1 | CPU a   | and Memory                     | 22 |

|     | 3.1.1   | CPU                            | 22 |

|     | 3.1.2   | Internal Memory                | 22 |

|     | 3.1.3   | External Flash and SRAM        | 23 |

|     | 3.1.4   | Memory Map                     | 23 |

| 3.2 | Timers  | s and Watchdogs                | 25 |

|     | 3.2.1   | 64-bit Timers                  | 25 |

|     | 3.2.2   | Watchdog Timers                | 25 |

| 3.3 |         | m Clocks                       | 26 |

|     | 3.3.1   | CPU Clock                      | 26 |

|     | 3.3.2   | RTC Clock                      | 26 |

|     | 3.3.3   | Audio PLL Clock                | 26 |

| 3.4 | Radio   |                                | 26 |

|     | 3.4.1   | 2.4 GHz Receiver               | 27 |

|     | 3.4.2   | 2.4 GHz Transmitter            | 27 |

|     | 3.4.3   | Clock Generator                | 27 |

| 3.5 | Wi-Fi   |                                | 27 |

|     | 3.5.1   | Wi-Fi Radio and Baseband       | 27 |

|     | 3.5.2   | Wi-Fi MAC                      | 28 |

| 3.6 | Blueto  |                                | 28 |

|     | 3.6.1   | Bluetooth Radio and Baseband   | 28 |

|     | 3.6.2 Bluetooth Interface                                 | 29 |

|-----|-----------------------------------------------------------|----|

|     | 3.6.3 Bluetooth Stack                                     | 29 |

|     | 3.6.4 Bluetooth Link Controller                           | 29 |

| 3.7 | RTC and Low-Power Management                              | 30 |

| 4   | Peripherals and Sensors                                   | 32 |

| 4.1 | Descriptions of Peripherals and Sensors                   | 32 |

|     | 4.1.1 General Purpose Input / Output Interface (GPIO)     | 32 |

|     | 4.1.2 Analog-to-Digital Converter (ADC)                   | 32 |

|     | 4.1.3 Hall Sensor                                         | 33 |

|     | 4.1.4 Digital-to-Analog Converter (DAC)                   | 33 |

|     | 4.1.5 Touch Sensor                                        | 33 |

|     | 4.1.6 Ultra-Low-Power Co-processor                        | 33 |

|     | 4.1.7 Ethernet MAC Interface                              | 34 |

|     | 4.1.8 SD/SDIO/MMC Host Controller                         | 34 |

|     | 4.1.9 SDIO/SPI Slave Controller                           | 34 |

|     | 4.1.10 Universal Asynchronous Receiver Transmitter (UART) | 35 |

|     | 4.1.11 I <sup>2</sup> C Interface                         | 35 |

|     | 4.1.12 I <sup>2</sup> S Interface                         | 35 |

|     | 4.1.13 Infrared Remote Controller                         | 35 |

|     | 4.1.14 Pulse Counter                                      | 35 |

|     | 4.1.15 Pulse Width Modulation (PWM)                       | 36 |

|     | 4.1.16 LED PWM                                            | 36 |

|     | 4.1.17 Serial Peripheral Interface (SPI)                  | 36 |

|     | 4.1.18 Accelerator                                        | 36 |

| 4.2 | Peripheral Pin Configurations                             | 37 |

| 5   | Electrical Characteristics                                | 42 |

| 5.1 | Absolute Maximum Ratings                                  | 42 |

| 5.2 | Recommended Operating Conditions                          | 42 |

| 5.3 | DC Characteristics (3.3 V, 25 °C)                         | 43 |

| 5.4 | Reliability Qualifications                                | 43 |

| 5.5 | RF Power-Consumption Specifications                       | 44 |

| 5.6 | Wi-Fi Radio                                               | 44 |

| 5.7 | Bluetooth Radio                                           | 45 |

|     | 5.7.1 Receiver – Basic Data Rate                          | 45 |

|     | 5.7.2 Transmitter – Basic Data Rate                       | 45 |

|     | 5.7.3 Receiver – Enhanced Data Rate                       | 46 |

|     | 5.7.4 Transmitter – Enhanced Data Rate                    | 46 |

| 5.8 | Bluetooth LE Radio                                        | 47 |

|     | 5.8.1 Receiver                                            | 47 |

|     | 5.8.2 Transmitter                                         | 47 |

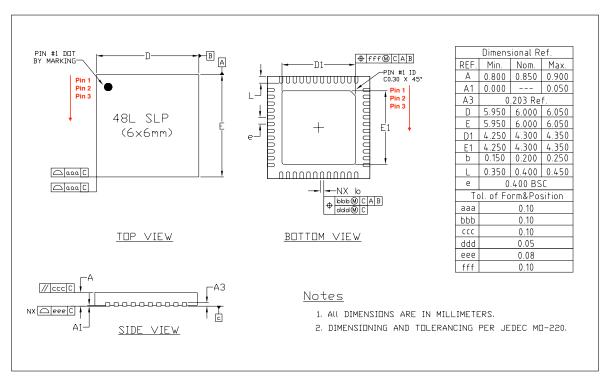

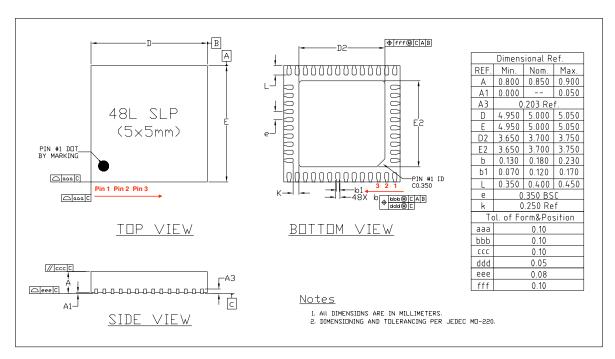

| 6   | Package Information                                       | 48 |

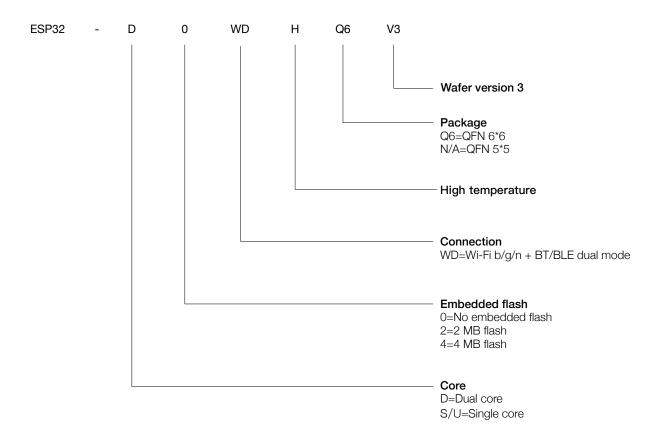

## 7 Part Number and Ordering Information

49

| 8    | Learning Resources          | 50 |

|------|-----------------------------|----|

| 8.1  | Must-Read Documents         | 50 |

| 8.2  | Must-Have Resources         | 50 |

| Ap   | opendix A – ESP32 Pin Lists | 51 |

| A.1. | Notes on ESP32 Pin Lists    | 51 |

| A.2. | . GPIO_Matrix               | 53 |

| A.3. | . Ethernet_MAC              | 58 |

| A.4. | . IO_MUX                    | 58 |

| Re   | evision History             | 60 |

## **List of Tables**

| 1  | Pin Description                                                      | 15 |

|----|----------------------------------------------------------------------|----|

| 2  | Description of ESP32 Power-up and Reset Timing Parameters            | 19 |

| 3  | Strapping Pins                                                       | 20 |

| 4  | Parameter Descriptions of Setup and Hold Times for the Strapping Pin | 21 |

| 5  | Memory and Peripheral Mapping                                        | 24 |

| 6  | Power Consumption by Power Modes                                     | 30 |

| 7  | ADC Characteristics                                                  | 32 |

| 8  | ADC Calibration Results                                              | 33 |

| 9  | Capacitive-Sensing GPIOs Available on ESP32                          | 33 |

| 10 | Peripheral Pin Configurations                                        | 37 |

| 11 | Absolute Maximum Ratings                                             | 42 |

| 12 | Recommended Operating Conditions                                     | 42 |

| 13 | DC Characteristics (3.3 V, 25 °C)                                    | 43 |

| 14 | Reliability Qualifications                                           | 43 |

| 15 | RF Power-Consumption Specifications                                  | 44 |

| 16 | Wi-Fi Radio Characteristics                                          | 44 |

| 17 | Receiver Characteristics – Basic Data Rate                           | 45 |

| 18 | Transmitter Characteristics – Basic Data Rate                        | 45 |

| 19 | Receiver Characteristics – Enhanced Data Rate                        | 46 |

| 20 | Transmitter Characteristics – Enhanced Data Rate                     | 46 |

| 21 | Receiver Characteristics – BLE                                       | 47 |

| 22 | Transmitter Characteristics – BLE                                    | 47 |

| 23 | ESP32 Ordering Information                                           | 49 |

| 24 | Notes on ESP32 Pin Lists                                             | 51 |

| 25 | GPIO_Matrix                                                          | 53 |

| 26 | Ethernet_MAC                                                         | 58 |

## List of Figures

| 1  | Functional Block Diagram                   | 12 |

|----|--------------------------------------------|----|

| 2  | ESP32 Pin Layout (QFN 6*6, Top View)       | 13 |

| 3  | ESP32 Pin Layout (QFN 5*5, Top View)       | 14 |

| 4  | ESP32 Power Scheme                         | 18 |

| 5  | ESP32 Power-up and Reset Timing            | 19 |

| 6  | Setup and Hold Times for the Strapping Pin | 21 |

| 7  | Address Mapping Structure                  | 23 |

| 8  | QFN48 (6x6 mm) Package                     | 48 |

| 9  | QFN48 (5x5 mm) Package                     | 48 |

| 10 | ESP32 Part Number                          | 49 |

## **1** Overview

ESP32 is a single 2.4 GHz Wi-Fi-and-Bluetooth combo chip designed with the TSMC ultra-low-power 40 nm technology. It is designed to achieve the best power and RF performance, showing robustness, versatility and reliability in a wide variety of applications and power scenarios.

The ESP32 series of chips includes ESP32-D0WD-V3, ESP32-D0WDQ6-V3, ESP32-D0WD, ESP32-D0WDQ6, ESP32-D2WD, ESP32-S0WD, and ESP32-U4WDH, among which, ESP32-D0WD-V3, ESP32-D0WDQ6-V3, and ESP32-U4WDH are based on ECO V3 wafer.

For details on part numbers and ordering information, please refer to Section 7.

For details on ECO V3 instructions, please refer to ESP32 ECO V3 User Guide.

### 1.1 Featured Solutions

### 1.1.1 Ultra-Low-Power Solution

ESP32 is designed for mobile, wearable electronics, and Internet-of-Things (IoT) applications. It features all the state-of-the-art characteristics of low-power chips, including fine-grained clock gating, multiple power modes, and dynamic power scaling. For instance, in a low-power IoT sensor hub application scenario, ESP32 is woken up periodically and only when a specified condition is detected. Low-duty cycle is used to minimize the amount of energy that the chip expends. The output of the power amplifier is also adjustable, thus contributing to an optimal trade-off between communication range, data rate and power consumption.

Note:

For more information, refer to Section 3.7 RTC and Low-Power Management.

### 1.1.2 Complete Integration Solution

ESP32 is a highly-integrated solution for Wi-Fi-and-Bluetooth IoT applications, with around 20 external components. ESP32 integrates an antenna switch, RF balun, power amplifier, low-noise receive amplifier, filters, and power management modules. As such, the entire solution occupies minimal Printed Circuit Board (PCB) area.

ESP32 uses CMOS for single-chip fully-integrated radio and baseband, while also integrating advanced calibration circuitries that allow the solution to remove external circuit imperfections or adjust to changes in external conditions. As such, the mass production of ESP32 solutions does not require expensive and specialized Wi-Fi testing equipment.

### 1.2 Wi-Fi Key Features

- 802.11 b/g/n

- 802.11 n (2.4 GHz), up to 150 Mbps

- WMM

- TX/RX A-MPDU, RX A-MSDU

- Immediate Block ACK

Espressif Systems

- Defragmentation

- Automatic Beacon monitoring (hardware TSF)

- 4 × virtual Wi-Fi interfaces

- Simultaneous support for Infrastructure Station, SoftAP, and Promiscuous modes Note that when ESP32 is in Station mode, performing a scan, the SoftAP channel will be changed.

- Antenna diversity

#### Note:

For more information, please refer to Section 3.5 Wi-Fi.

### 1.3 BT Key Features

- Compliant with Bluetooth v4.2 BR/EDR and BLE specifications

- Class-1, class-2 and class-3 transmitter without external power amplifier

- Enhanced Power Control

- +12 dBm transmitting power

- NZIF receiver with –94 dBm BLE sensitivity

- Adaptive Frequency Hopping (AFH)

- Standard HCI based on SDIO/SPI/UART

- High-speed UART HCI, up to 4 Mbps

- Bluetooth 4.2 BR/EDR BLE dual mode controller

- Synchronous Connection-Oriented/Extended (SCO/eSCO)

- CVSD and SBC for audio codec

- Bluetooth Piconet and Scatternet

- Multi-connections in Classic BT and BLE

- Simultaneous advertising and scanning

### 1.4 MCU and Advanced Features

### 1.4.1 CPU and Memory

- Xtensa<sup>®</sup> single-/dual-core 32-bit LX6 microprocessor(s), up to 600 MIPS (200 MIPS for ESP32-S0WD/ESP32-U4WDH, 400 MIPS for ESP32-D2WD)

- 448 KB ROM

- 520 KB SRAM

- 16 KB SRAM in RTC

- QSPI supports multiple flash/SRAM chips

### 1.4.2 Clocks and Timers

- Internal 8 MHz oscillator with calibration

- Internal RC oscillator with calibration

- External 2 MHz ~ 60 MHz crystal oscillator (40 MHz only for Wi-Fi/BT functionality)

- External 32 kHz crystal oscillator for RTC with calibration

- Two timer groups, including 2 × 64-bit timers and 1 × main watchdog in each group

- One RTC timer

- RTC watchdog

### 1.4.3 Advanced Peripheral Interfaces

- 34 × programmable GPIOs

- 12-bit SAR ADC up to 18 channels

- 2 × 8-bit DAC

- 10 × touch sensors

- 4 × SPI

- 2 × I<sup>2</sup>S

- 2 × I<sup>2</sup>C

- 3 × UART

- 1 host (SD/eMMC/SDIO)

- 1 slave (SDIO/SPI)

- Ethernet MAC interface with dedicated DMA and IEEE 1588 support

- Two-Wire Automotive Interface (TWAI<sup>®</sup>, compatible with ISO11898-1)

- IR (TX/RX)

- Motor PWM

- LED PWM up to 16 channels

- Hall sensor

### 1.4.4 Security

- Secure boot

- Flash encryption

- 1024-bit OTP, up to 768-bit for customers

- Cryptographic hardware acceleration:

- AES

- Hash (SHA-2)

- RSA

- ECC

- Random Number Generator (RNG)

### 1.5 Applications (A Non-exhaustive List)

- Generic Low-power IoT Sensor Hub

- Generic Low-power IoT Data Loggers

- Cameras for Video Streaming

- Over-the-top (OTT) Devices

- Speech Recognition

- Image Recognition

- Mesh Network

- Home Automation

- Light control

- Smart plugs

- Smart door locks

- Smart Building

- Smart lighting

- Energy monitoring

- Industrial Automation

- Industrial wireless control

- Industrial robotics

- Smart Agriculture

- Smart greenhouses

- Smart irrigation

- Agriculture robotics

- Audio Applications

- Internet music players

- Live streaming devices

- Internet radio players

- Audio headsets

- Health Care Applications

- Health monitoring

- Baby monitors

- Wi-Fi-enabled Toys

- Remote control toys

- Proximity sensing toys

- Educational toys

- Wearable Electronics

- Smart watches

- Smart bracelets

- Retail & Catering Applications

- POS machines

- Service robots

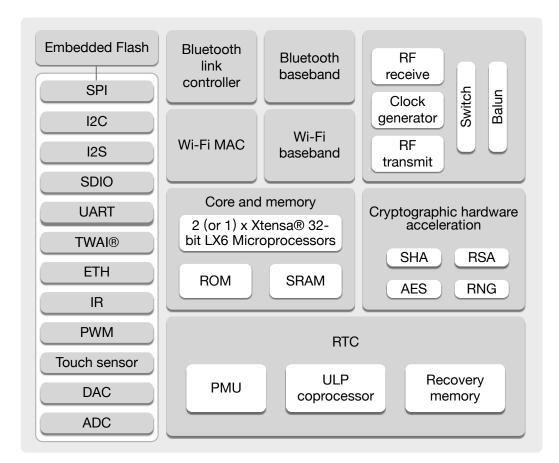

### 1.6 Block Diagram

#### Figure 1: Functional Block Diagram

#### Note:

Products in the ESP32 series differ from each other in terms of their support for embedded flash and the number of CPUs they have. For details, please refer to Section 7 *Part Number and Ordering Information*.

## 2 Pin Definitions

### 2.1 Pin Layout

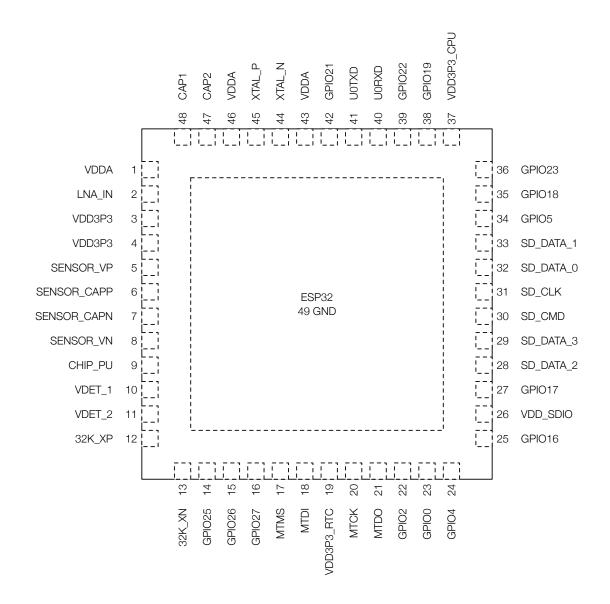

Figure 2: ESP32 Pin Layout (QFN 6\*6, Top View)

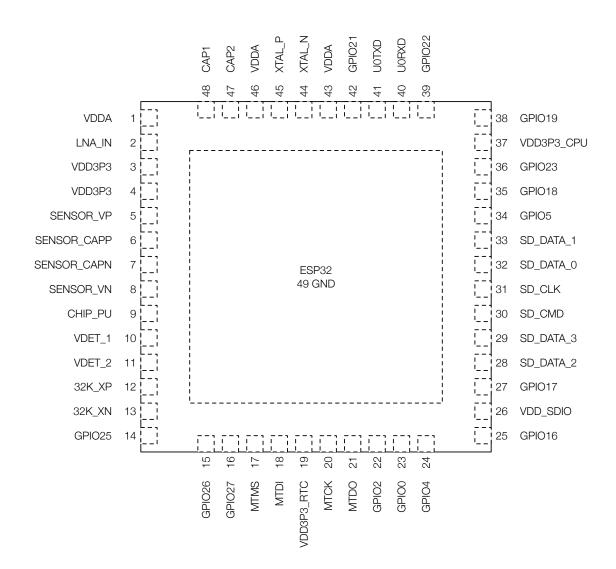

#### Figure 3: ESP32 Pin Layout (QFN 5\*5, Top View)

#### Note:

For details on ESP32's part numbers and the corresponding packaging, please refer to Section 7 Part Number and Ordering Information.

### 2.2 Pin Description

#### Table 1: Pin Description

| Name No. Type Function |                                                |     |                                                                                    |  |  |  |  |  |  |  |

|------------------------|------------------------------------------------|-----|------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                        |                                                |     | Analog                                                                             |  |  |  |  |  |  |  |

| VDDA                   | VDDA1PAnalog power supply (2.3 V $\sim$ 3.6 V) |     |                                                                                    |  |  |  |  |  |  |  |

| LNA_IN                 | 2                                              | I/O | RF input and output                                                                |  |  |  |  |  |  |  |

| VDD3P3                 | 3                                              | Р   | Analog power supply (2.3 V $\sim$ 3.6 V)                                           |  |  |  |  |  |  |  |

| VDD3P3                 | 4                                              | Р   | Analog power supply (2.3 V $\sim$ 3.6 V)                                           |  |  |  |  |  |  |  |

|                        |                                                |     | VDD3P3_RTC                                                                         |  |  |  |  |  |  |  |

| SENSOR_VP              | 5                                              | I   | GPIO36, ADC1_CH0, RTC_GPIO0                                                        |  |  |  |  |  |  |  |

| SENSOR_CAPP            | 6                                              | Ι   | GPIO37, ADC1_CH1, RTC_GPIO1                                                        |  |  |  |  |  |  |  |

| SENSOR_CAPN            | 7                                              | Ι   | GPIO38, ADC1_CH2, RTC_GPIO2                                                        |  |  |  |  |  |  |  |

| SENSOR_VN              | 8                                              | Ι   | GPIO39, ADC1_CH3, RTC_GPIO3                                                        |  |  |  |  |  |  |  |

|                        |                                                |     | h: On; enables the chip                                                            |  |  |  |  |  |  |  |

| CHIP_PU                | 9                                              | I   | Low: Off; the chip powers off                                                      |  |  |  |  |  |  |  |

|                        |                                                |     | Note: Do not leave the CHIP_PU pin floating.                                       |  |  |  |  |  |  |  |

| VDET_1                 | 10                                             | I   | GPIO34, ADC1_CH6, RTC_GPIO4                                                        |  |  |  |  |  |  |  |

| VDET_2                 | 11                                             | I   | GPIO35, ADC1_CH7, RTC_GPIO5                                                        |  |  |  |  |  |  |  |

| 32K_XP                 | 12                                             | I/O | GPIO32, ADC1_CH4, RTC_GPIO9, TOUCH9, 32K_XP (32.768 kHz crystal oscillator input)  |  |  |  |  |  |  |  |

| 32K_XN                 | 13                                             | I/O | GPIO33, ADC1_CH5, RTC_GPIO8, TOUCH8, 32K_XN (32.768 kHz crystal oscillator output) |  |  |  |  |  |  |  |

| GPIO25                 | 14                                             | I/O | GPIO25, ADC2_CH8, RTC_GPIO6, DAC_1, EMAC_RXD0                                      |  |  |  |  |  |  |  |

| GPIO26                 | 15                                             | I/O | GPIO26, ADC2_CH9, RTC_GPIO7, DAC_2, EMAC_RXD1                                      |  |  |  |  |  |  |  |

| GPIO27                 | 16                                             | I/O | GPIO27, ADC2_CH7, RTC_GPIO17, TOUCH7, EMAC_RX_DV                                   |  |  |  |  |  |  |  |

| MTMS                   | 17                                             | I/O | GPIO14, ADC2_CH6, RTC_GPIO16, TOUCH6, EMAC_TXD2, HSPICLK, HS2_CLK, SD_CLK, MTMS    |  |  |  |  |  |  |  |

| MTDI                   | 18                                             | I/O | GPIO12, ADC2_CH5, RTC_GPIO15, TOUCH5, EMAC_TXD3, HSPIQ, HS2_DATA2, SD_DATA2, MTDI  |  |  |  |  |  |  |  |

| VDD3P3_RTC             | 19                                             | Р   | Input power supply for RTC IO (2.3 V $\sim$ 3.6 V)                                 |  |  |  |  |  |  |  |

| MTCK                   | 20                                             | I/O | GPIO13, ADC2_CH4, RTC_GPIO14, TOUCH4, EMAC_RX_ER, HSPID, HS2_DATA3, SD_DATA3, MTCK |  |  |  |  |  |  |  |

| MTDO                   | 21                                             | I/O | GPIO15, ADC2_CH3, RTC_GPIO13, TOUCH3, EMAC_RXD3, HSPICS0, HS2_CMD, SD_CMD, MTDO    |  |  |  |  |  |  |  |

| Name       | No. | Туре | Function   |                   |                       |                         |                      |          |            |          |

|------------|-----|------|------------|-------------------|-----------------------|-------------------------|----------------------|----------|------------|----------|

| GPIO2      | 22  | I/O  | GPIO2,     | ADC2_CH2,         | RTC_GPIO12,           | TOUCH2,                 |                      | HSPIWP,  | HS2_DATA0, | SD_DATA0 |

| GPIO0      | 23  | I/O  | GPIO0,     | ADC2_CH1,         | RTC_GPIO11,           | TOUCH1,                 | EMAC_TX_CLK,         | CLK_OUT1 | ,          |          |

| GPIO4      | 24  | I/O  | GPIO4,     | ADC2_CH0,         | RTC_GPIO10,           | TOUCH0,                 | EMAC_TX_ER,          | HSPIHD,  | HS2_DATA1, | SD_DATA1 |

|            |     |      |            |                   | VE                    | DD_SDIO                 |                      |          |            |          |

| GPIO16     | 25  | I/O  | GPIO16,    | HS1_DATA4,        | U2RXD,                | EMAC_CLK_               | OUT                  |          |            |          |

| VDD_SDIO   | 26  | Р    | Output po  | ower supply: 1.8  | 3 V or the same v     | oltage as VDD           | 03P3_RTC             |          |            |          |

| GPIO17     | 27  | I/O  | GPIO17,    | HS1_DATA5,        | U2TXD,                | EMAC_CLK_               | OUT_180              |          |            |          |

| SD_DATA_2  | 28  | I/O  | GPIO9,     | HS1_DATA2,        | U1RXD,                | SD_DATA2,               | SPIHD                |          |            |          |

| SD_DATA_3  | 29  | I/O  | GPIO10,    | HS1_DATA3,        | U1TXD,                | SD_DATA3,               | SPIWP                |          |            |          |

| SD_CMD     | 30  | I/O  | GPIO11,    | HS1_CMD,          | U1RTS,                | SD_CMD,                 | SPICS0               |          |            |          |

| SD_CLK     | 31  | I/O  | GPIO6,     | HS1_CLK,          | U1CTS,                | SD_CLK,                 | SPICLK               |          |            |          |

| SD_DATA_0  | 32  | I/O  | GPIO7,     | HS1_DATA0,        | U2RTS,                | SD_DATA0,               | SPIQ                 |          |            |          |

| SD_DATA_1  | 33  | I/O  | GPIO8,     | HS1_DATA1,        | U2CTS,                | SD_DATA1,               | SPID                 |          |            |          |

|            |     |      |            |                   | VDE                   | 03P3_CPU                |                      |          |            |          |

| GPIO5      | 34  | I/O  | GPIO5,     | HS1_DATA6,        | VSPICS0,              | EMAC_RX_C               | LK                   |          |            |          |

| GPIO18     | 35  | I/O  | GPIO18,    | HS1_DATA7,        | VSPICLK               |                         |                      |          |            |          |

| GPIO23     | 36  | I/O  | GPIO23,    | HS1_STROBE,       | , VSPID               |                         |                      |          |            |          |

| VDD3P3_CPU | 37  | Р    | Input pow  | ver supply for CF | PU IO (1.8 V $\sim$ 3 | .6 V)                   |                      |          |            |          |

| GPIO19     | 38  | I/O  | GPIO19,    | UOCTS,            | VSPIQ,                | EMAC_TXD0               |                      |          |            |          |

| GPIO22     | 39  | I/O  | GPIO22,    | UORTS,            | VSPIWP,               | EMAC_TXD1               |                      |          |            |          |

| UORXD      | 40  | I/O  | GPIO3,     | UORXD,            | CLK_OUT2              |                         |                      |          |            |          |

| UOTXD      | 41  | I/O  | GPIO1,     | U0TXD,            | CLK_OUT3,             | EMAC_RXD2               |                      |          |            |          |

| GPIO21     | 42  | I/O  | GPIO21,    |                   | VSPIHD,               | EMAC_TX_EI              | N                    |          |            |          |

|            |     |      |            |                   |                       | Analog                  |                      |          |            |          |

| VDDA       | 43  | Р    | Analog po  | ower supply (2.3  | $V\sim 3.6~\text{V})$ |                         |                      |          |            |          |

| XTAL_N     | 44  | 0    | External c | crystal output    |                       |                         |                      |          |            |          |

| XTAL_P     | 45  |      | External c | rystal input      |                       |                         |                      |          |            |          |

| VDDA       | 46  | Р    | Analog po  | ower supply (2.3  | $V\sim 3.6$ V)        |                         |                      |          |            |          |

| CAP2       | 47  |      | Connects   | to a 3.3 nF (109  | %) capacitor and      | l 20 k $\Omega$ resisto | r in parallel to CAF | 21       |            |          |

| Name | No. | Туре | Function                                       |

|------|-----|------|------------------------------------------------|

| CAP1 | 48  |      | Connects to a 10 nF series capacitor to ground |

| GND  | 49  | Р    | Ground                                         |

Note:

- The pin-pin mapping between ESP32-D2WD/ESP32-U4WDH and the embedded flash is as follows: GPIO16 = CS#, GPIO17 = IO1/DO, SD\_CMD = IO3/HOLD#, SD\_CLK = CLK, SD\_DATA\_0 = IO2/WP#, SD\_DATA\_1 = IO0/DI. The pins used for embedded flash are not recommended for other uses.

- In most cases, the data port connection between ESP32 series of chips other than ESP32-D2WD/ESP32-U4WDH and external flash is as follows: SD\_DATA0/SPIQ = IO1/DO, SD\_DATA1/SPID = IO0/DI, SD\_DATA2/SPIHD = IO3/HOLD#, SD\_DATA3/SPIWP = IO2/WP#.

- For a quick reference guide to using the IO\_MUX, Ethernet MAC, and GIPO Matrix pins of ESP32, please refer to Appendix ESP32 Pin Lists.

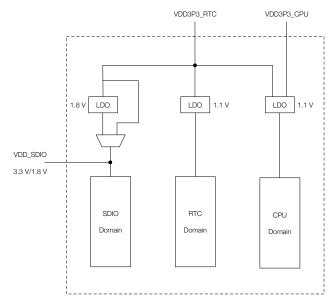

### 2.3 Power Scheme

ESP32's digital pins are divided into three different power domains:

- VDD3P3\_RTC

- VDD3P3\_CPU

- VDD\_SDIO

VDD3P3\_RTC is also the input power supply for RTC and CPU.

VDD3P3\_CPU is also the input power supply for CPU.

VDD\_SDIO connects to the output of an internal LDO whose input is VDD3P3\_RTC. When VDD\_SDIO is connected to the same PCB net together with VDD3P3\_RTC, the internal LDO is disabled automatically. The power scheme diagram is shown below:

Figure 4: ESP32 Power Scheme

The internal LDO can be configured as having 1.8 V, or the same voltage as VDD3P3\_RTC. It can be powered off via software to minimize the current of flash/SRAM during the Deep-sleep mode.

#### Notes on CHIP\_PU:

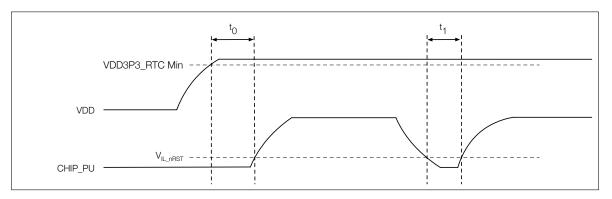

• The illustration below shows the ESP32 power-up and reset timing. Details about the parameters are listed in Table 2.

Figure 5: ESP32 Power-up and Reset Timing

| Table 2: Description of ESP32 Power-up and Reset Timing Parameters |

|--------------------------------------------------------------------|

|--------------------------------------------------------------------|

| Parameters     | Description                                                                                                            | Min. | Unit |

|----------------|------------------------------------------------------------------------------------------------------------------------|------|------|

| t <sub>0</sub> | Time between the 3.3 V rails being brought up and CHIP_PU being activated                                              | 50   | μs   |

| t <sub>1</sub> | Duration of CHIP_PU signal level $< V_{IL_nRST}$ (refer to its value in Table 13 DC Characteristics) to reset the chip | 50   | μs   |

In scenarios where ESP32 is powered on and off repeatedly by switching the power rails, while there is a

large capacitor on the VDD33 rail and CHIP\_PU and VDD33 are connected, simply switching off the

CHIP\_PU power rail and immediately switching it back on may cause an incomplete power discharge cycle

and failure to reset the chip adequately.

An additional discharge circuit may be required to accelerate the discharge of the large capacitor on rail VDD33, which will ensure proper power-on-reset when the ESP32 is powered up again. Please find the discharge circuit in Figure **ESP32-WROOM-32 Peripheral Schematics**, in *ESP32-WROOM-32 Datasheet*.

When a battery is used as the power supply for the ESP32 series of chips and modules, a supply voltage supervisor is recommended, so that a boot failure due to low voltage is avoided. Users are recommended to pull CHIP\_PU low if the power supply for ESP32 is below 2.3 V. For the reset circuit, please refer to Figure ESP32-WROOM-32 Peripheral Schematics, in *ESP32-WROOM-32 Datasheet*.

#### Notes on power supply:

- The operating voltage of ESP32 ranges from 2.3 V to 3.6 V. When using a single-power supply, the recommended voltage of the power supply is 3.3 V, and its recommended output current is 500 mA or more.

- When VDD\_SDIO 1.8 V is used as the power supply for external flash/PSRAM, a 2-kohm grounding resistor should be added to VDD\_SDIO. For the circuit design, please refer to Figure ESP32-WROVER Schematics, in ESP32-WROVER Datasheet.

- When the three digital power supplies are used to drive peripherals, e.g., 3.3 V flash, they should comply with the peripherals' specifications.

### 2.4 Strapping Pins

There are five strapping pins:

• MTDI

- GPI00

- GPIO2

- MTDO

- GPI05

Software can read the values of these five bits from register "GPIO\_STRAPPING".

During the chip's system reset release (power-on-reset, RTC watchdog reset and brownout reset), the latches of the strapping pins sample the voltage level as strapping bits of "0" or "1", and hold these bits until the chip is powered down or shut down. The strapping bits configure the device's boot mode, the operating voltage of VDD\_SDIO and other initial system settings.

Each strapping pin is connected to its internal pull-up/pull-down during the chip reset. Consequently, if a strapping pin is unconnected or the connected external circuit is high-impedance, the internal weak pull-up/pull-down will determine the default input level of the strapping pins.

To change the strapping bit values, users can apply the external pull-down/pull-up resistances, or use the host MCU's GPIOs to control the voltage level of these pins when powering on the chip.

After reset release, the strapping pins work as normal-function pins.

Refer to Table 3 for a detailed boot-mode configuration by strapping pins.

| Voltage of Internal LDO (VDD_SDIO) |                |                 |                  |                |             |  |  |  |

|------------------------------------|----------------|-----------------|------------------|----------------|-------------|--|--|--|

| Pin                                | Default        | 3.3             | 3 V              | 1.8 V          |             |  |  |  |

| MTDI                               | Pull-down      | (               | )                | -              | 1           |  |  |  |

|                                    |                | Bo              | oting Mode       |                |             |  |  |  |

| Pin                                | Default        | SPI             | Boot             | Downlo         | ad Boot     |  |  |  |

| GPIO0                              | Pull-up        | -               | 1                | (              | )           |  |  |  |

| GPIO2                              | Pull-down      | Don't           | -care            | (              | )           |  |  |  |

| E                                  | Enabling/Disal | bling Debugging | g Log Print over | U0TXD During I | Booting     |  |  |  |

| Pin                                | Default        | UOTXD           | Active           | UOTXE          | ) Silent    |  |  |  |

| MTDO                               | Pull-up        | -               | 1                | (              | )           |  |  |  |

|                                    |                | Timinę          | g of SDIO Slave  |                |             |  |  |  |

|                                    |                | FE Sampling     | FE Sampling      | RE Sampling    | RE Sampling |  |  |  |

| Pin                                | Default        | FE Output       | RE Output        | FE Output      | RE Output   |  |  |  |

| MTDO                               | Pull-up        | 0               | 0                | 1              | 1           |  |  |  |

| GPIO5                              | Pull-up        | 0               | 1                | 0              | 1           |  |  |  |

#### Table 3: Strapping Pins

#### Note:

- FE: falling-edge, RE: rising-edge.

- Firmware can configure register bits to change the settings of "Voltage of Internal LDO (VDD\_SDIO)" and "Timing of SDIO Slave", after booting.

- For ESP32 chips that contain an embedded flash, users need to note the logic level of MTDI. For example, ESP32-D2WD contains an embedded flash that operates at 1.8 V, therefore, the MTDI should be pulled high. ESP32-U4WDH contains an embedded flash that operates at 3.3 V, therefore, the MTDI should be low.

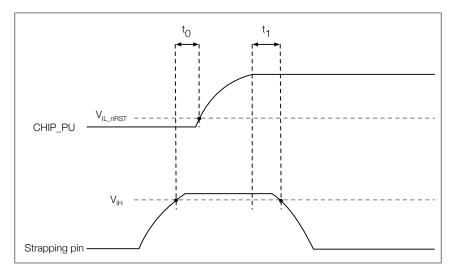

The illustration below shows the setup and hold times for the strapping pin before and after the CHIP\_PU signal goes high. Details about the parameters are listed in Table 4.

Figure 6: Setup and Hold Times for the Strapping Pin

#### Table 4: Parameter Descriptions of Setup and Hold Times for the Strapping Pin

| Parameters     | Description                                     | Min. | Unit |

|----------------|-------------------------------------------------|------|------|

| to             | Setup time before CHIP_PU goes from low to high | 0    | ms   |

| t <sub>1</sub> | Hold time after CHIP_PU goes high               | 1    | ms   |

## 3 Functional Description

This chapter describes the functions integrated in ESP32.

### 3.1 CPU and Memory

### 3.1.1 CPU

ESP32 contains one or two low-power Xtensa<sup>®</sup> 32-bit LX6 microprocessor(s) with the following features:

- 7-stage pipeline to support the clock frequency of up to 240 MHz (160 MHz for ESP32-S0WD, ESP32-D2WD, and ESP32-U4WDH)

- 16/24-bit Instruction Set provides high code-density

- Support for Floating Point Unit

- Support for DSP instructions, such as a 32-bit multiplier, a 32-bit divider, and a 40-bit MAC

- Support for 32 interrupt vectors from about 70 interrupt sources

The single-/dual-CPU interfaces include:

- Xtensa RAM/ROM Interface for instructions and data

- Xtensa Local Memory Interface for fast peripheral register access

- External and internal interrupt sources

- JTAG for debugging

### 3.1.2 Internal Memory

ESP32's internal memory includes:

- 448 KB of ROM for booting and core functions

- 520 KB of on-chip SRAM for data and instructions

- 8 KB of SRAM in RTC, which is called RTC FAST Memory and can be used for data storage; it is accessed by the main CPU during RTC Boot from the Deep-sleep mode.

- 8 KB of SRAM in RTC, which is called RTC SLOW Memory and can be accessed by the co-processor during the Deep-sleep mode.

- 1 Kbit of eFuse: 256 bits are used for the system (MAC address and chip configuration) and the remaining 768 bits are reserved for customer applications, including flash-encryption and chip-ID.

- Embedded flash

#### Note:

Products in the ESP32 series differ from each other, in terms of their support for embedded flash and the size of it. For details, please refer to Section 7 *Part Number and Ordering Information*.

### 3.1.3 External Flash and SRAM

ESP32 supports multiple external QSPI flash and SRAM chips. More details can be found in Chapter SPI in the *ESP32 Technical Reference Manual*. ESP32 also supports hardware encryption/decryption based on AES to protect developers' programs and data in flash.

ESP32 can access the external QSPI flash and SRAM through high-speed caches.

- Up to 16 MB of external flash can be mapped into CPU instruction memory space and read-only memory space simultaneously.

- When external flash is mapped into CPU instruction memory space, up to 11 MB + 248 KB can be mapped at a time. Note that if more than 3 MB + 248 KB are mapped, cache performance will be reduced due to speculative reads by the CPU.

- When external flash is mapped into read-only data memory space, up to 4 MB can be mapped at a time. 8-bit, 16-bit and 32-bit reads are supported.

- External SRAM can be mapped into CPU data memory space. SRAM up to 8 MB is supported and up to 4 MB can be mapped at a time. 8-bit, 16-bit and 32-bit reads and writes are supported.

#### Note:

After ESP32 is initialized, firmware can customize the mapping of external SRAM or flash into the CPU address space.

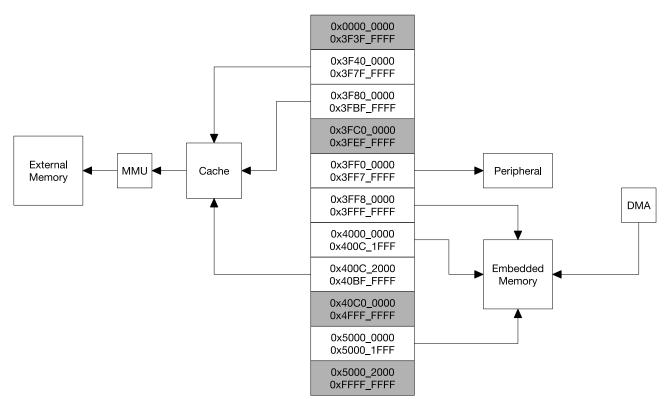

### 3.1.4 Memory Map

The structure of address mapping is shown in Figure 7. The memory and peripheral mapping of ESP32 is shown in Table 5.

Figure 7: Address Mapping Structure

| Category   | Target           | Start Address   | End Address     | Size         |

|------------|------------------|-----------------|-----------------|--------------|

| concego.y  | Internal ROM 0   | 0x4000_0000     | 0x4005_FFFF     | 384 KB       |

|            | Internal ROM 1   | 0x3FF9_0000     | 0x3FF9_FFFF     | 64 KB        |

|            | Internal SRAM 0  | 0x4007_0000     | 0x4009_FFFF     | 192 KB       |

|            |                  | 0x3FFE_0000     | 0x3FFF_FFF      |              |

| Embedded   | Internal SRAM 1  | <br>0x400A_0000 | <br>0x400B_FFFF | – 128 KB     |

| Memory     | Internal SRAM 2  | 0x3FFA_E000     | 0x3FFD_FFFF     | 200 KB       |

|            |                  | 0x3FF8_0000     | 0x3FF8_1FFF     |              |

|            | RTC FAST Memory  | 0x400C_0000     | 0x400C_1FFF     | - 8 KB       |

|            | RTC SLOW Memory  | 0x5000_0000     | 0x5000_1FFF     | 8 KB         |

|            |                  | 0x3F40_0000     | 0x3F7F_FFFF     | 4 MB         |

| External   | External Flash   | 0x400C_2000     | 0x40BF_FFFF     | 11 MB+248 KB |

| Memory     | External RAM     | 0x3F80_0000     | 0x3FBF_FFFF     | 4 MB         |

|            | DPort Register   | 0x3FF0_0000     | 0x3FF0_0FFF     | 4 KB         |

|            | AES Accelerator  | 0x3FF0_1000     | 0x3FF0_1FFF     | 4 KB         |

|            | RSA Accelerator  | 0x3FF0_2000     | 0x3FF0_2FFF     | 4 KB         |

|            | SHA Accelerator  | 0x3FF0_3000     | 0x3FF0_3FFF     | 4 KB         |

|            | Secure Boot      | 0x3FF0_4000     | 0x3FF0_4FFF     | 4 KB         |

|            | Cache MMU Table  | 0x3FF1_0000     | 0x3FF1_3FFF     | 16 KB        |

|            | PID Controller   | 0x3FF1_F000     | 0x3FF1_FFFF     | 4 KB         |

|            | UART0            | 0x3FF4_0000     | 0x3FF4_0FFF     | 4 KB         |

|            | SPI1             | 0x3FF4_2000     | 0x3FF4_2FFF     | 4 KB         |

|            | SPI0             | 0x3FF4_3000     | 0x3FF4_3FFF     | 4 KB         |

|            | GPIO             | 0x3FF4_4000     | 0x3FF4_4FFF     | 4 KB         |

|            | RTC              | 0x3FF4_8000     | 0x3FF4_8FFF     | 4 KB         |

|            | IO MUX           | 0x3FF4_9000     | 0x3FF4_9FFF     | 4 KB         |

|            | SDIO Slave       | 0x3FF4_B000     | 0x3FF4_BFFF     | 4 KB         |

|            | UDMA1            | 0x3FF4_C000     | 0x3FF4_CFFF     | 4 KB         |

| Peripheral | I2S0             | 0x3FF4_F000     | 0x3FF4_FFFF     | 4 KB         |

|            | UART1            | 0x3FF5_0000     | 0x3FF5_0FFF     | 4 KB         |

|            | 12C0             | 0x3FF5_3000     | 0x3FF5_3FFF     | 4 KB         |

|            | UDMA0            | 0x3FF5_4000     | 0x3FF5_4FFF     | 4 KB         |

|            | SDIO Slave       | 0x3FF5_5000     | 0x3FF5_5FFF     | 4 KB         |

|            | RMT              | 0x3FF5_6000     | 0x3FF5_6FFF     | 4 KB         |

|            | PCNT             | 0x3FF5_7000     | 0x3FF5_7FFF     | 4 KB         |

|            | SDIO Slave       | 0x3FF5_8000     | 0x3FF5_8FFF     | 4 KB         |

|            | LED PWM          | 0x3FF5_9000     | 0x3FF5_9FFF     | 4 KB         |

|            | eFuse Controller | 0x3FF5_A000     | 0x3FF5_AFFF     | 4 KB         |

|            | Flash Encryption | 0x3FF5_B000     | 0x3FF5_BFFF     | 4 KB         |

|            | PWM0             | 0x3FF5_E000     | 0x3FF5_EFFF     | 4 KB         |

|            | TIMG0            | 0x3FF5_F000     | 0x3FF5_FFFF     | 4 KB         |

|            | TIMG1            | 0x3FF6_0000     | 0x3FF6_0FFF     | 4 KB         |

|            | SPI2             | 0x3FF6_4000     | 0x3FF6_4FFF     | 4 KB         |

|            | SPI3             | 0x3FF6_5000     | 0x3FF6_5FFF     | 4 KB         |

### Table 5: Memory and Peripheral Mapping

| Category   | Target | Start Address | End Address | Size |

|------------|--------|---------------|-------------|------|

|            | SYSCON | 0x3FF6_6000   | 0x3FF6_6FFF | 4 KB |

|            | I2C1   | 0x3FF6_7000   | 0x3FF6_7FFF | 4 KB |

|            | SDMMC  | 0x3FF6_8000   | 0x3FF6_8FFF | 4 KB |

|            | EMAC   | 0x3FF6_9000   | 0x3FF6_AFFF | 8 KB |

| Peripheral | PWM1   | 0x3FF6_C000   | 0x3FF6_CFFF | 4 KB |

|            | I2S1   | 0x3FF6_D000   | 0x3FF6_DFFF | 4 KB |

|            | UART2  | 0x3FF6_E000   | 0x3FF6_EFFF | 4 KB |

|            | PWM2   | 0x3FF6_F000   | 0x3FF6_FFFF | 4 KB |

|            | PWM3   | 0x3FF7_0000   | 0x3FF7_0FFF | 4 KB |

|            | RNG    | 0x3FF7_5000   | 0x3FF7_5FFF | 4 KB |

### 3.2 Timers and Watchdogs

### 3.2.1 64-bit Timers

There are four general-purpose timers embedded in the chip. They are all 64-bit generic timers which are based on 16-bit prescalers and 64-bit auto-reload-capable up/down-timers.

The timers feature:

- A 16-bit clock prescaler, from 2 to 65536

- A 64-bit timer

- Configurable up/down timer: incrementing or decrementing

- Halt and resume of time-base counter

- Auto-reload at alarming

- Software-controlled instant reload

- Level and edge interrupt generation

### 3.2.2 Watchdog Timers

The chip has three watchdog timers: one in each of the two timer modules (called the Main Watchdog Timer, or MWDT) and one in the RTC module (called the RTC Watchdog Timer, or RWDT). These watchdog timers are intended to recover from an unforeseen fault causing the application program to abandon its normal sequence. A watchdog timer has four stages. Each stage may trigger one of three or four possible actions upon the expiry of its programmed time period, unless the watchdog is fed or disabled. The actions are: interrupt, CPU reset, core reset, and system reset. Only the RWDT can trigger the system reset, and is able to reset the entire chip, including the RTC itself. A timeout value can be set for each stage individually.

During flash boot the RWDT and the first MWDT start automatically in order to detect, and recover from, booting problems.

The watchdogs have the following features:

- Four stages, each of which can be configured or disabled separately

- A programmable time period for each stage

- One of three or four possible actions (interrupt, CPU reset, core reset, and system reset) upon the expiry of each stage

- 32-bit expiry counter

- Write protection that prevents the RWDT and MWDT configuration from being inadvertently altered

- SPI flash boot protection

If the boot process from an SPI flash does not complete within a predetermined time period, the watchdog will reboot the entire system.

### 3.3 System Clocks

#### 3.3.1 CPU Clock

Upon reset, an external crystal clock source is selected as the default CPU clock. The external crystal clock source also connects to a PLL to generate a high-frequency clock (typically 160 MHz).

In addition, ESP32 has an internal 8 MHz oscillator. The application can select the clock source from the external crystal clock source, the PLL clock or the internal 8 MHz oscillator. The selected clock source drives the CPU clock directly, or after division, depending on the application.

### 3.3.2 RTC Clock

The RTC clock has five possible sources:

- external low-speed (32 kHz) crystal clock

- external crystal clock divided by 4

- internal RC oscillator (typically about 150 kHz, and adjustable)

- internal 8 MHz oscillator

- internal 31.25 kHz clock (derived from the internal 8 MHz oscillator divided by 256)

When the chip is in the normal power mode and needs faster CPU accessing, the application can choose the external high-speed crystal clock divided by 4 or the internal 8 MHz oscillator. When the chip operates in the low-power mode, the application chooses the external low-speed (32 kHz) crystal clock, the internal RC clock or the internal 31.25 kHz clock.

### 3.3.3 Audio PLL Clock

The audio clock is generated by the ultra-low-noise fractional-N PLL. More details can be found in Chapter Reset and Clock in the *ESP32 Technical Reference Manual*.

### 3.4 Radio

The radio module consists of the following blocks:

- 2.4 GHz receiver

- 2.4 GHz transmitter

- bias and regulators

- balun and transmit-receive switch

- clock generator

### 3.4.1 2.4 GHz Receiver

The 2.4 GHz receiver demodulates the 2.4 GHz RF signal to quadrature baseband signals and converts them to the digital domain with two high-resolution, high-speed ADCs. To adapt to varying signal channel conditions, RF filters, Automatic Gain Control (AGC), DC offset cancelation circuits and baseband filters are integrated in the chip.

### 3.4.2 2.4 GHz Transmitter

The 2.4 GHz transmitter modulates the quadrature baseband signals to the 2.4 GHz RF signal, and drives the antenna with a high-powered Complementary Metal Oxide Semiconductor (CMOS) power amplifier. The use of digital calibration further improves the linearity of the power amplifier, enabling state-of-the-art performance in delivering up to +20.5 dBm of power for an 802.11b transmission and +18 dBm for an 802.11n transmission.

Additional calibrations are integrated to cancel any radio imperfections, such as:

- Carrier leakage

- I/Q phase matching

- Baseband nonlinearities

- RF nonlinearities

- Antenna matching

These built-in calibration routines reduce the amount of time required for product testing, and render the testing equipment unnecessary.

### 3.4.3 Clock Generator

The clock generator produces quadrature clock signals of 2.4 GHz for both the receiver and the transmitter. All components of the clock generator are integrated into the chip, including all inductors, varactors, filters, regulators and dividers.

The clock generator has built-in calibration and self-test circuits. Quadrature clock phases and phase noise are optimized on-chip with patented calibration algorithms which ensure the best performance of the receiver and the transmitter.

### 3.5 Wi-Fi

ESP32 implements a TCP/IP and full 802.11 b/g/n Wi-Fi MAC protocol. It supports the Basic Service Set (BSS) STA and SoftAP operations under the Distributed Control Function (DCF). Power management is handled with minimal host interaction to minimize the active-duty period.

### 3.5.1 Wi-Fi Radio and Baseband

The ESP32 Wi-Fi Radio and Baseband support the following features:

- 802.11b/g/n

- 802.11n MCS0-7 in both 20 MHz and 40 MHz bandwidth

- 802.11n MCS32 (RX)

- 802.11n 0.4  $\mu$ s guard-interval

- up to 150 Mbps of data rate

- Receiving STBC 2×1

- Up to 20.5 dBm of transmitting power

- Adjustable transmitting power

- Antenna diversity

ESP32 supports antenna diversity with an external RF switch. One or more GPIOs control the RF switch and selects the best antenna to minimize the effects of channel fading.

### 3.5.2 Wi-Fi MAC

The ESP32 Wi-Fi MAC applies low-level protocol functions automatically. They are as follows:

- 4 × virtual Wi-Fi interfaces

- Simultaneous Infrastructure BSS Station mode/SoftAP mode/Promiscuous mode

- RTS protection, CTS protection, Immediate Block ACK

- Defragmentation

- TX/RX A-MPDU, RX A-MSDU

- TXOP

- WMM

- CCMP (CBC-MAC, counter mode), TKIP (MIC, RC4), WAPI (SMS4), WEP (RC4) and CRC

- Automatic beacon monitoring (hardware TSF)

### 3.6 Bluetooth

The chip integrates a Bluetooth link controller and Bluetooth baseband, which carry out the baseband protocols and other low-level link routines, such as modulation/demodulation, packet processing, bit stream processing, frequency hopping, etc.

### 3.6.1 Bluetooth Radio and Baseband

The Bluetooth Radio and Baseband support the following features:

- Class-1, class-2 and class-3 transmit output powers, and a dynamic control range of up to 24 dB

- $\pi/4$  DQPSK and 8 DPSK modulation

- High performance in NZIF receiver sensitivity with over 94 dBm of dynamic range

- Class-1 operation without external PA

- Internal SRAM allows full-speed data-transfer, mixed voice and data, and full piconet operation

- Logic for forward error correction, header error control, access code correlation, CRC, demodulation, encryption bit stream generation, whitening and transmit pulse shaping

- ACL, SCO, eSCO and AFH

- A-law,  $\mu$ -law and CVSD digital audio CODEC in PCM interface

- SBC audio CODEC

- Power management for low-power applications

- SMP with 128-bit AES

#### 3.6.2 Bluetooth Interface

- Provides UART HCI interface, up to 4 Mbps

- Provides SDIO / SPI HCI interface

- Provides PCM / I2S audio interface

### 3.6.3 Bluetooth Stack

The Bluetooth stack of the chip is compliant with the Bluetooth v4.2 BR/EDR and Bluetooth LE specifications.

### 3.6.4 Bluetooth Link Controller

The link controller operates in three major states: standby, connection and sniff. It enables multiple connections, and other operations, such as inquiry, page, and secure simple-pairing, and therefore enables Piconet and Scatternet. Below are the features:

- Classic Bluetooth

- Device Discovery (inquiry, and inquiry scan)

- Connection establishment (page, and page scan)

- Multi-connections

- Asynchronous data reception and transmission

- Synchronous links (SCO/eSCO)

- Master/Slave Switch

- Adaptive Frequency Hopping and Channel assessment

- Broadcast encryption

- Authentication and encryption

- Secure Simple-Pairing

- Multi-point and scatternet management

- Sniff mode

- Connectionless Slave Broadcast (transmitter and receiver)

- Enhanced power control

Espressif Systems

- Ping

- Bluetooth Low Energy

- Advertising

- Scanning

- Simultaneous advertising and scanning

- Multiple connections

- Asynchronous data reception and transmission

- Adaptive Frequency Hopping and Channel assessment

- Connection parameter update

- Data Length Extension

- Link Layer Encryption

- LE Ping

### 3.7 RTC and Low-Power Management

With the use of advanced power-management technologies, ESP32 can switch between different power modes.

- Power modes

- Active mode: The chip radio is powered on. The chip can receive, transmit, or listen.

- Modem-sleep mode: The CPU is operational and the clock is configurable. The Wi-Fi/Bluetooth baseband and radio are disabled.

- Light-sleep mode: The CPU is paused. The RTC memory and RTC peripherals, as well as the ULP co-processor are running. Any wake-up events (MAC, host, RTC timer, or external interrupts) will wake up the chip.

- **Deep-sleep mode**: Only the RTC memory and RTC peripherals are powered on. Wi-Fi and Bluetooth connection data are stored in the RTC memory. The ULP co-processor is functional.

- Hibernation mode: The internal 8-MHz oscillator and ULP co-processor are disabled. The RTC recovery memory is powered down. Only one RTC timer on the slow clock and certain RTC GPIOs are active. The RTC timer or the RTC GPIOs can wake up the chip from the Hibernation mode.

| Power mode          | Description                                                              |                        |                     | Power consumption |

|---------------------|--------------------------------------------------------------------------|------------------------|---------------------|-------------------|

|                     | Wi-Fi Tx packet           tive (RF working)           Wi-Fi/BT Tx packet |                        |                     | Please refer to   |

| Active (RF working) |                                                                          |                        | Wi-Fi/BT Tx packet  |                   |

|                     |                                                                          | Wi-Fi/BT Rx and listen |                     |                   |

|                     |                                                                          | *<br>240 MHz           | Dual-core chip(s)   | 30 mA ~ 68 mA     |

|                     |                                                                          |                        | Single-core chip(s) | N/A               |

| Modem-sleep         | The CPU is                                                               | 160 MHz                | Dual-core chip(s)   | 27 mA ~ 44 mA     |

| wouern-sieep        | powered on.                                                              |                        | Single-core chip(s) | 27 mA ~ 34 mA     |

#### Table 6: Power Consumption by Power Modes

| Power mode  | Description                          | Power consumption   |               |

|-------------|--------------------------------------|---------------------|---------------|

|             | Normal speed: 80 MHz                 | Dual-core chip(s)   | 20 mA ~ 31 mA |

|             |                                      | Single-core chip(s) | 20 mA ~ 25 mA |

| Light-sleep | -                                    | 0.8 mA              |               |

|             | The ULP co-processor is pov          | 150 μA              |               |

| Deep-sleep  | ULP sensor-monitored p               | 100 µA @1% duty     |               |

|             | RTC timer + RTC mem                  | 10 µA               |               |

| Hibernation | RTC timer only                       | 5 μΑ                |               |

| Power off   | CHIP_PU is set to low level, the chi | 1 μΑ                |               |

#### Note:

- \* Among the ESP32 series of SoCs, ESP32-D0WD-V3, ESP32-D0WDQ6-V3, ESP32-D0WD, and ESP32-D0WDQ6 have a maximum CPU frequency of 240 MHz, ESP32-D2WD, ESP32-S0WD, and ESP32-U4WDH have a maximum CPU frequency of 160 MHz.

- When Wi-Fi is enabled, the chip switches between Active and Modem-sleep modes. Therefore, power consumption changes accordingly.

- In Modem-sleep mode, the CPU frequency changes automatically. The frequency depends on the CPU load and the peripherals used.

- During Deep-sleep, when the ULP co-processor is powered on, peripherals such as GPIO and I<sup>2</sup>C are able to operate.

- When the system works in the ULP sensor-monitored pattern, the ULP co-processor works with the ULP sensor periodically and the ADC works with a duty cycle of 1%, so the power consumption is 100  $\mu$ A.

## 4 Peripherals and Sensors

### 4.1 Descriptions of Peripherals and Sensors

### 4.1.1 General Purpose Input / Output Interface (GPIO)

ESP32 has 34 GPIO pins which can be assigned various functions by programming the appropriate registers. There are several kinds of GPIOs: digital-only, analog-enabled, capacitive-touch-enabled, etc. Analog-enabled GPIOs and Capacitive-touch-enabled GPIOs can be configured as digital GPIOs.

Most of the digital GPIOs can be configured as internal pull-up or pull-down, or set to high impedance. When configured as an input, the input value can be read through the register. The input can also be set to edge-trigger or level-trigger to generate CPU interrupts. Most of the digital IO pins are bi-directional, non-inverting and tristate, including input and output buffers with tristate control. These pins can be multiplexed with other functions, such as the SDIO, UART, SPI, etc. (More details can be found in the Appendix, Table IO\_MUX.) For low-power operations, the GPIOs can be set to hold their states.

### 4.1.2 Analog-to-Digital Converter (ADC)

ESP32 integrates 12-bit SAR ADCs and supports measurements on 18 channels (analog-enabled pins). The ULP-coprocessor in ESP32 is also designed to measure voltage, while operating in the sleep mode, which enables low-power consumption. The CPU can be woken up by a threshold setting and/or via other triggers.

With appropriate settings, the ADCs can be configured to measure voltage on 18 pins maximum.

Table 7 describes the ADC characteristics.

| Parameter                       | Description                                 | Min | Max | Unit |

|---------------------------------|---------------------------------------------|-----|-----|------|

| DNL (Differential nonlinearity) | RTC controller; ADC connected to an         | -7  | 7   | LSB  |

|                                 | external 100 nF capacitor; DC signal input; | -/  | 1   | LOD  |

| INL (Integral nonlinearity)     | ambient temperature at 25 °C;               | -12 | 12  | I SB |

| INC (Integral nonlinearity)     | Wi-Fi&BT off                                | -12 | 12  | LOD  |

| Compling rate                   | RTC controller                              | _   | 200 | ksps |

| Sampling rate                   | DIG controller                              | -   | 2   | Msps |

#### Table 7: ADC Characteristics

#### Notes:

- When atten=3 and the measurement result is above 3000 (voltage at approx. 2450 mV), the ADC accuracy will be worse than described in the table above.

- To get better DNL results, users can take multiple sampling tests with a filter, or calculate the average value.

- The input voltage range of GPIO pins within VDD3P3\_RTC domain should strictly follow the DC characteristics provided in Table 13. Otherwise, measurement errors may be introduced, and chip performance may be affected.

By default, there are  $\pm 6\%$  differences in measured results between chips. ESP-IDF provides couple of <u>calibration</u> <u>methods</u> for ADC1. Results after calibration using eFuse Vref value are shown in Table 8. For higher accuracy, users may apply other calibration methods provided in ESP-IDF, or implement their own.

| Parameter   | Description                                                | Min | Max | Unit |

|-------------|------------------------------------------------------------|-----|-----|------|

|             | Atten=0, effective measurement range of 100 $\sim$ 950 mV  | -23 | 23  | mV   |

| Total error | Atten=1, effective measurement range of 100 $\sim$ 1250 mV | -30 | 30  | mV   |

| TOLAI EITOI | Atten=2, effective measurement range of 150 $\sim$ 1750 mV | -40 | 40  | mV   |

|             | Atten=3, effective measurement range of 150 $\sim$ 2450 mV | -60 | 60  | mV   |

#### Table 8: ADC Calibration Results

#### 4.1.3 Hall Sensor

ESP32 integrates a Hall sensor based on an N-carrier resistor. When the chip is in the magnetic field, the Hall sensor develops a small voltage laterally on the resistor, which can be directly measured by the ADC.

### 4.1.4 Digital-to-Analog Converter (DAC)

Two 8-bit DAC channels can be used to convert two digital signals into two analog voltage signal outputs. The design structure is composed of integrated resistor strings and a buffer. This dual DAC supports power supply as input voltage reference. The two DAC channels can also support independent conversions.

### 4.1.5 Touch Sensor

ESP32 has 10 capacitive-sensing GPIOs, which detect variations induced by touching or approaching the GPIOs with a finger or other objects. The low-noise nature of the design and the high sensitivity of the circuit allow relatively small pads to be used. Arrays of pads can also be used, so that a larger area or more points can be detected. The 10 capacitive-sensing GPIOs are listed in Table 9.

| Capacitive-sensing signal name | Pin name |

|--------------------------------|----------|

| ТО                             | GPIO4    |

| T1                             | GPIO0    |

| T2                             | GPIO2    |

| ТЗ                             | MTDO     |

| Τ4                             | MTCK     |

| Т5                             | MTDI     |

| Т6                             | MTMS     |

| Т7                             | GPIO27   |

| Т8                             | 32K_XN   |

| Т9                             | 32K_XP   |

#### Table 9: Capacitive-Sensing GPIOs Available on ESP32

### 4.1.6 Ultra-Low-Power Co-processor

The ULP processor and RTC memory remain powered on during the Deep-sleep mode. Hence, the developer can store a program for the ULP processor in the RTC slow memory to access the peripheral devices, internal timers and internal sensors during the Deep-sleep mode. This is useful for designing applications where the CPU needs to be woken up by an external event, or a timer, or a combination of the two, while maintaining minimal power consumption.

### 4.1.7 Ethernet MAC Interface

An IEEE-802.3-2008-compliant Media Access Controller (MAC) is provided for Ethernet LAN communications. ESP32 requires an external physical interface device (PHY) to connect to the physical LAN bus (twisted-pair, fiber, etc.). The PHY is connected to ESP32 through 17 signals of MII or nine signals of RMII. The following features are supported on the Ethernet MAC (EMAC) interface:

- 10 Mbps and 100 Mbps rates

- Dedicated DMA controller allowing high-speed transfer between the dedicated SRAM and Ethernet MAC

- Tagged MAC frame (VLAN support)

- Half-duplex (CSMA/CD) and full-duplex operation

- MAC control sublayer (control frames)

- 32-bit CRC generation and removal

- Several address-filtering modes for physical and multicast address (multicast and group addresses)

- 32-bit status code for each transmitted or received frame

- Internal FIFOs to buffer transmit and receive frames. The transmit FIFO and the receive FIFO are both 512 words (32-bit)

- Hardware PTP (Precision Time Protocol) in accordance with IEEE 1588 2008 (PTP V2)

- 25 MHz/50 MHz clock output

### 4.1.8 SD/SDIO/MMC Host Controller

An SD/SDIO/MMC host controller is available on ESP32, which supports the following features:

- Secure Digital memory (SD mem Version 3.0 and Version 3.01)

- Secure Digital I/O (SDIO Version 3.0)

- Consumer Electronics Advanced Transport Architecture (CE-ATA Version 1.1)

- Multimedia Cards (MMC Version 4.41, eMMC Version 4.5 and Version 4.51)

The controller allows up to 80 MHz clock output in three different data-bus modes: 1-bit, 4-bit and 8-bit. It supports two SD/SDIO/MMC4.41 cards in a 4-bit data-bus mode. It also supports one SD card operating at 1.8 V.

### 4.1.9 SDIO/SPI Slave Controller

ESP32 integrates an SD device interface that conforms to the industry-standard SDIO Card Specification Version 2.0, and allows a host controller to access the SoC, using the SDIO bus interface and protocol. ESP32 acts as the slave on the SDIO bus. The host can access the SDIO-interface registers directly and can access shared memory via a DMA engine, thus maximizing performance without engaging the processor cores.

The SDIO/SPI slave controller supports the following features:

- SPI, 1-bit SDIO, and 4-bit SDIO transfer modes over the full clock range from 0 to 50 MHz

- Configurable sampling and driving clock edge

- Special registers for direct access by host

- Interrupts to host for initiating data transfer

- Automatic loading of SDIO bus data and automatic discarding of padding data

- Block size of up to 512 bytes

- Interrupt vectors between the host and the slave, allowing both to interrupt each other

- Supports DMA for data transfer

### 4.1.10 Universal Asynchronous Receiver Transmitter (UART)

ESP32 has three UART interfaces, i.e., UART0, UART1 and UART2, which provide asynchronous communication (RS232 and RS485) and IrDA support, communicating at a speed of up to 5 Mbps. UART provides hardware management of the CTS and RTS signals and software flow control (XON and XOFF). All of the interfaces can be accessed by the DMA controller or directly by the CPU.

### 4.1.11 I<sup>2</sup>C Interface

ESP32 has two I<sup>2</sup>C bus interfaces which can serve as I<sup>2</sup>C master or slave, depending on the user's configuration. The I<sup>2</sup>C interfaces support:

- Standard mode (100 Kbit/s)

- Fast mode (400 Kbit/s)

- Up to 5 MHz, yet constrained by SDA pull-up strength

- 7-bit/10-bit addressing mode

- Dual addressing mode

Users can program command registers to control I<sup>2</sup>C interfaces, so that they have more flexibility.

### 4.1.12 I<sup>2</sup>S Interface

Two standard I<sup>2</sup>S interfaces are available in ESP32. They can be operated in master or slave mode, in full duplex and half-duplex communication modes, and can be configured to operate with an 8-/16-/32-/48-/64-bit resolution as input or output channels. BCK clock frequency, from 10 kHz up to 40 MHz, is supported. When one or both of the I<sup>2</sup>S interfaces are configured in the master mode, the master clock can be output to the external DAC/CODEC.

Both of the I<sup>2</sup>S interfaces have dedicated DMA controllers. PDM and BT PCM interfaces are supported.

### 4.1.13 Infrared Remote Controller

The infrared remote controller supports eight channels of infrared remote transmission and receiving. By programming the pulse waveform, it supports various infrared protocols. Eight channels share a 512 x 32-bit block of memory to store the transmitting or receiving waveform.

### 4.1.14 Pulse Counter

The pulse counter captures pulse and counts pulse edges through seven modes. It has eight channels, each of which captures four signals at a time. The four input signals include two pulse signals and two control signals. When the counter reaches a defined threshold, an interrupt is generated.

### 4.1.15 Pulse Width Modulation (PWM)

The Pulse Width Modulation (PWM) controller can be used for driving digital motors and smart lights. The controller consists of PWM timers, the PWM operator and a dedicated capture sub-module. Each timer provides timing in synchronous or independent form, and each PWM operator generates a waveform for one PWM channel. The dedicated capture sub-module can accurately capture events with external timing.

#### 4.1.16 LED PWM

The LED PWM controller can generate 16 independent channels of digital waveforms with configurable periods and duties.

The 16 channels of digital waveforms operate with an APB clock of 80 MHz. Eight of these channels have the option of using the 8 MHz oscillator clock. Each channel can select a 20-bit timer with configurable counting range, while its accuracy of duty can be up to 16 bits within a 1 ms period.

The software can change the duty immediately. Moreover, each channel automatically supports step-by-step duty increase or decrease, which is useful for the LED RGB color-gradient generator.

### 4.1.17 Serial Peripheral Interface (SPI)

ESP32 features three SPIs (SPI, HSPI and VSPI) in slave and master modes in 1-line full-duplex and 1/2/4-line half-duplex communication modes. These SPIs also support the following general-purpose SPI features:

- Four modes of SPI transfer format, which depend on the polarity (CPOL) and the phase (CPHA) of the SPI clock

- Up to 80 MHz (The actual speed it can reach depends on the selected pads, PCB tracing, peripheral characteristics, etc.)

- up to 64-byte FIFO

All SPIs can also be connected to the external flash/SRAM and LCD. Each SPI can be served by DMA controllers.

### 4.1.18 Accelerator

ESP32 is equipped with hardware accelerators of general algorithms, such as AES (FIPS PUB 197), SHA (FIPS PUB 180-4), RSA, and ECC, which support independent arithmetic, such as Big Integer Multiplication and Big Integer Modular Multiplication. The maximum operation length for RSA, ECC, Big Integer Multiply and Big Integer Modular Multiplication is 4096 bits.

The hardware accelerators greatly improve operation speed and reduce software complexity. They also support code encryption and dynamic decryption, which ensures that code in the flash will not be hacked.

# 4.2 Peripheral Pin Configurations

#### Table 10: Peripheral Pin Configurations

| Interface    | Signal   | Pin         | Function                    |

|--------------|----------|-------------|-----------------------------|

|              | ADC1_CH0 | SENSOR_VP   |                             |

|              | ADC1_CH1 | SENSOR_CAPP |                             |

|              | ADC1_CH2 | SENSOR_CAPN |                             |

|              | ADC1_CH3 | SENSOR_VN   |                             |

|              | ADC1_CH4 | 32K_XP      |                             |

|              | ADC1_CH5 | 32K_XN      |                             |

|              | ADC1_CH6 | VDET_1      |                             |

|              | ADC1_CH7 | VDET_2      |                             |

| 400          | ADC2_CH0 | GPIO4       |                             |

| ADC          | ADC2_CH1 | GPIO0       | Two 12-bit SAR ADCs         |

|              | ADC2_CH2 | GPIO2       |                             |

|              | ADC2_CH3 | MTDO        |                             |

|              | ADC2_CH4 | MTCK        |                             |

|              | ADC2_CH5 | MTDI        |                             |

|              | ADC2_CH6 | MTMS        |                             |

|              | ADC2_CH7 | GPIO27      |                             |

|              | ADC2_CH8 | GPIO25      |                             |

|              | ADC2_CH9 | GPIO26      |                             |

| 540          | DAC_1    | GPIO25      | T 012 D40                   |

| DAC          | DAC_2    | GPIO26      | Two 8-bit DACs              |

|              | TOUCH0   | GPIO4       |                             |

|              | TOUCH1   | GPIO0       |                             |

|              | TOUCH2   | GPIO2       |                             |

|              | TOUCH3   | MTDO        |                             |

|              | TOUCH4   | MTCK        |                             |

| Touch Sensor | TOUCH5   | MTDI        | Capacitive touch sensors    |

|              | TOUCH6   | MTMS        |                             |

|              | TOUCH7   | GPIO27      |                             |

|              | TOUCH8   | 32K_XN      |                             |

|              | ТОИСН9   | 32K_XP      |                             |

|              | MTDI     | MTDI        |                             |

|              | MTCK     | MTCK        |                             |

| JTAG         | MTMS     | MTMS        | JTAG for software debugging |

|              | MTDO     | MTDO        |                             |

| Interface        | Signal          | Pin           | Function                                             |  |  |

|------------------|-----------------|---------------|------------------------------------------------------|--|--|

|                  | HS2_CLK         | MTMS          |                                                      |  |  |

|                  | HS2_CMD         | MTDO          | -                                                    |  |  |

| SD/SDIO/MMC Host | HS2_DATA0       | GPIO2         |                                                      |  |  |

| Controller       | HS2_DATA1       | GPIO4         | - Supports SD memory card V3.01 standard             |  |  |

|                  | HS2_DATA2       | MTDI          |                                                      |  |  |

|                  | HS2_DATA3       | MTCK          |                                                      |  |  |

|                  | PWM0_OUT0~2     |               |                                                      |  |  |

|                  | PWM1_OUT_IN0~2  |               | Three channels of 16 bit timera concrete             |  |  |

|                  | PWM0_FLT_IN0~2  |               | Three channels of 16-bit timers generate             |  |  |

| Motor D\A/NA     | PWM1_FLT_IN0~2  |               | PWM waveforms. Each channel has a pair               |  |  |

| Motor PWM        | PWM0_CAP_IN0~2  | Any GPIO Pins | of output signals, three fault detection             |  |  |

|                  | PWM1_CAP_IN0~2  |               | signals, three event-capture signals, and            |  |  |

|                  | PWM0_SYNC_IN0~2 |               | three sync signals.                                  |  |  |

|                  | PWM1_SYNC_IN0~2 |               |                                                      |  |  |

|                  | SD_CLK          | MTMS          |                                                      |  |  |

|                  | SD_CMD          | MTDO          | SDIO interface that conforms to the                  |  |  |

| SDIO/SPI Slave   | SD_DATA0        | GPIO2         | industry standard SDIO 2.0 card                      |  |  |

| Controller       | SD_DATA1        | GPIO4         | specification                                        |  |  |

|                  | SD_DATA2        | MTDI          | specification                                        |  |  |

|                  | SD_DATA3        | MTCK          |                                                      |  |  |

|                  | U0RXD_in        |               |                                                      |  |  |

|                  | U0CTS_in        |               |                                                      |  |  |

|                  | U0DSR_in        |               |                                                      |  |  |

|                  | U0TXD_out       |               |                                                      |  |  |

|                  | U0RTS_out       |               |                                                      |  |  |