# 300 mA, Low Voltage, Low Quiescent Current LDO Regulator

#### **Features**

- · Passes Automotive AEC-Q100 Reliability Testing

- · 300 mA Output Current Capability

- Input Operating Voltage Range: 2.1V to 6.0V

- Adjustable Output Voltage Range: 0.8V to 5.0V (MCP1824 only)

- · Standard Fixed Output Voltages:

- 0.8V, 1.2V, 1.8V, 2.5V, 3.0V, 3.3V, 5.0V

- Other Fixed Output Voltage Options Available Upon Request

- · Low Dropout Voltage: 200 mV Typical at 300 mA

- Typical Output Voltage Tolerance: 0.4%

- Stable with 1.0 µF Ceramic Output Capacitor

- · Fast Response to Load Transients

- Low Supply Current: 120 μA (typical)

- Low Shutdown Supply Current: 0.1 µA (typical) (MCP1824 only)

- Fixed Delay on Power Good Output (MCP1824 only)

- Short Circuit Current Limiting and Overtemperature Protection

- 5-Lead Plastic SOT-223, SOT-23 Package Options (MCP1824)

- 3-Lead Plastic SOT-223 Package Option (MCP1824S)

#### **Applications**

- · High-Speed Driver Chipset Power

- · Networking Backplane Cards

- · Notebook Computers

- Network Interface Cards

- · Palmtop Computers

- · 2.5V to 1.XV Regulators

#### **Description**

The MCP1824/MCP1824S is a 300 mA Low Dropout (LDO) linear regulator that provides high current and low output voltages. The MCP1824 comes in a fixed or adjustable output voltage version, with an output voltage range of 0.8V to 5.0V. The 300 mA output current capability, combined with the low output voltage capability, make the MCP1824 a good choice for new sub-1.8V output voltage LDO applications that have high current demands. The MCP1824S is a 3-pin fixed voltage version.

The MCP1824/MCP1824S is stable using ceramic output capacitors that inherently provide lower output noise and reduce the size and cost of the entire regulator solution. Only 1  $\mu F$  of output capacitance is needed to stabilize the LDO.

Using CMOS construction, the quiescent current consumed by the MCP1824/MCP1824S is typically less than 120  $\mu$ A over the entire input voltage range, making it attractive for portable computing applications that demand high output current. The MCP1824 versions have a Shutdown (SHDN) pin. When shut down, the quiescent current is reduced to less than 0.1  $\mu$ A.

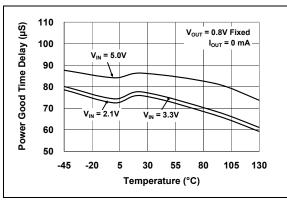

On the MCP1824 fixed output versions, the scaled-down output voltage is internally monitored and a power good (PWRGD) output is provided when the output is within 92% of regulation (typical). The PWRGD delay is internally fixed at 110 µs (typical).

The overtemperature and short circuit current-limiting provide additional protection for the LDO during system fault conditions.

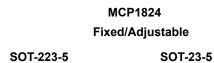

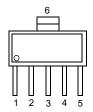

# **Package Types**

|     | SOT              | -223             | SOT-23           |                  |  |

|-----|------------------|------------------|------------------|------------------|--|

| Pin | Fixed Adjustable |                  | Fixed            | Adjustable       |  |

| 1   | SHDN             | SHDN             | V <sub>IN</sub>  | V <sub>IN</sub>  |  |

| 2   | $V_{IN}$         | V <sub>IN</sub>  | GND (TAB)        | GND (TAB)        |  |

| 3   | GND (TAB)        | GND (TAB)        | SHDN             | SHDN             |  |

| 4   | V <sub>OUT</sub> | V <sub>OUT</sub> | PWRGD            | ADJ              |  |

| 5   | PWRGD            | ADJ              | V <sub>OUT</sub> | V <sub>OUT</sub> |  |

| 6   | GND (TAB)        | GND (TAB)        | _                | _                |  |

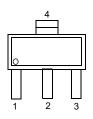

MCP1824S

SOT-223-3

| Pin | SOT-223          |

|-----|------------------|

| 1   | V <sub>IN</sub>  |

| 2   | GND (TAB)        |

| 3   | V <sub>OUT</sub> |

| 4   | GND (TAB)        |

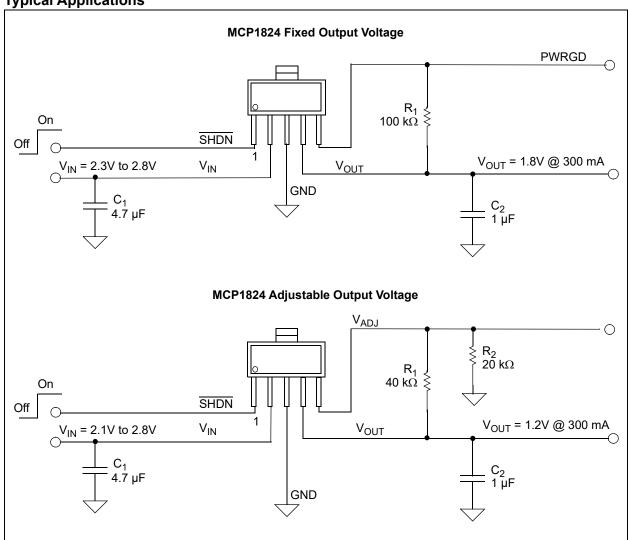

# **Typical Applications**

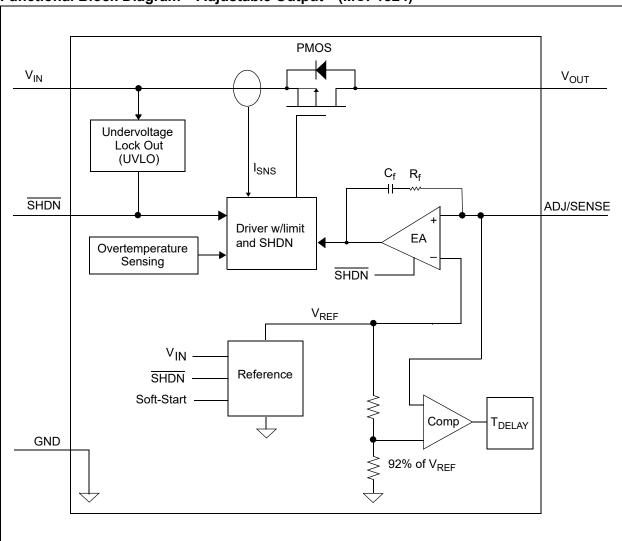

# Functional Block Diagram - Adjustable Output (MCP1824)

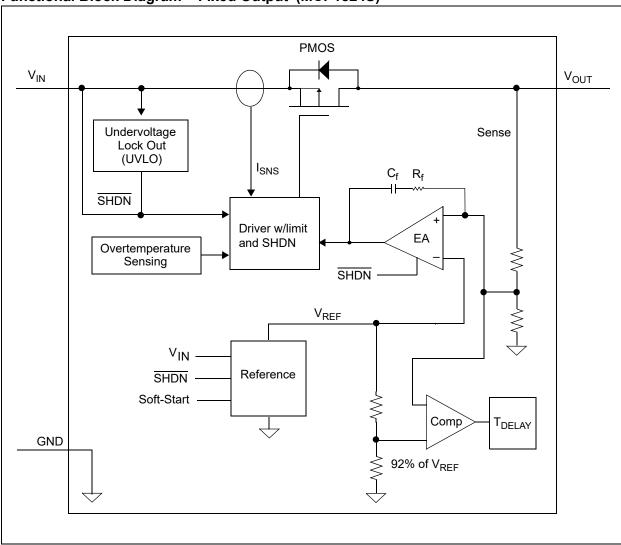

# Functional Block Diagram - Fixed Output (MCP1824S)

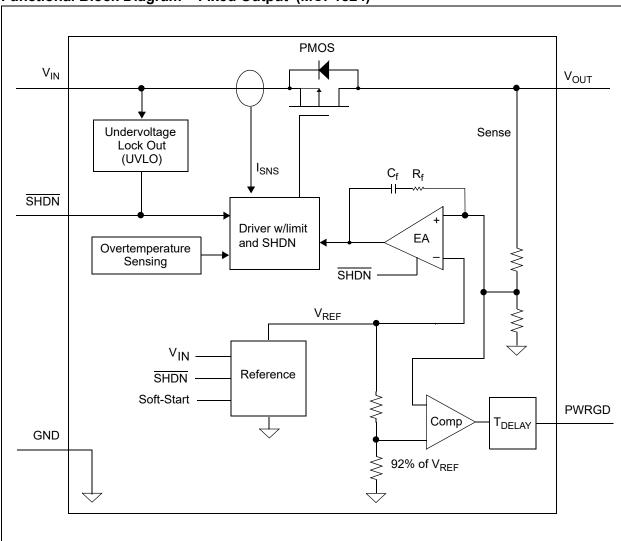

# Functional Block Diagram - Fixed Output (MCP1824)

### 1.0 ELECTRICAL CHARACTERISTICS

# Absolute Maximum Ratings<sup>†</sup>

| Input Voltage, V <sub>IN</sub>                 | 6.5V                                |

|------------------------------------------------|-------------------------------------|

| Maximum Voltage on Any Pin                     | $(GND - 0.3V)$ to $(V_{IN} + 0.3)V$ |

| Maximum Power Dissipation                      | Internally-Limited <sup>(1)</sup>   |

| Output Short Circuit Duration                  |                                     |

| Storage Temperature                            | –65°C to +150°C                     |

| Maximum Junction Temperature, T <sub>J</sub>   | +150°C                              |

| Operating Junction Temperature, T <sub>J</sub> | 40°C to +125°C                      |

| ESD Protection on All Pins <sup>(2)</sup> :    |                                     |

| HBM                                            | ±4 kV                               |

| MM                                             | ±400 V                              |

| CDM                                            | ±2 kV                               |

- † Notice: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- Note 1: The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction temperature and the thermal resistance from junction to air. (i.e., T<sub>A</sub>, T<sub>J</sub>, θ<sub>JA</sub>). Exceeding the maximum allowable power dissipation will cause the device operating junction temperature to exceed the maximum +150°C rating. Sustained junction temperatures above 150°C can impact device reliability.

- 2: Testing was performed according to AEC-Q100 Standard. ESD CDM was tested on the 5L SOT-223 package. For additional information please contact your local Microchip sales office.

# **AC/DC CHARACTERISTICS**

**Electrical Specifications:** Unless otherwise noted,  $V_{IN} = V_{OUT(MAX)} + V_{DROPOUT(MAX)}$ , **Note 1**,  $V_R = 1.8V$  for Adjustable Output,  $I_{OUT} = 1$  mA,  $C_{IN} = C_{OUT} = 4.7$   $\mu$ F (X7R Ceramic),  $T_A = +25$ °C. **Boldface** type applies for junction temperatures,  $T_J$  (**Note 6**) of **-40**°C to +125°C

| 71 11 ,                               | 31 11 3 1 7 0( 7                                              |     |       |               |       |                                                                 |  |  |

|---------------------------------------|---------------------------------------------------------------|-----|-------|---------------|-------|-----------------------------------------------------------------|--|--|

| Parameters                            | Sym                                                           | Min | Тур   | Max           | Units | Conditions                                                      |  |  |

| Input Operating Voltage               | V <sub>IN</sub>                                               | 2.1 | _     | 6.0           | V     |                                                                 |  |  |

| Output Voltage Range                  | V <sub>OUT</sub>                                              | 0.8 | _     | 5.0           | V     |                                                                 |  |  |

| Input Quiescent Current               | I <sub>q</sub>                                                | _   | 120   | 220           | μA    | I <sub>L</sub> = 0 mA, V <sub>OUT</sub> = 0.8V to 5.0V          |  |  |

| Input Quiescent Current for SHDN Mode | I <sub>SHDN</sub>                                             | _   | 0.1   | 3             | μA    | SHDN = GND                                                      |  |  |

| Maximum Continuous Output<br>Current  | I <sub>OUT</sub>                                              | 300 | _     | _             | mA    | V <sub>IN</sub> = 2.1V to 6.0V<br>V <sub>R</sub> = 0.8V to 5.0V |  |  |

| Line Regulation                       | ΔV <sub>OUT</sub> /<br>(V <sub>OUT</sub> x ΔV <sub>IN</sub> ) | _   | ±0.05 | ±0. <b>17</b> | %/V   | (Note 1) ≤ V <sub>IN</sub> ≤ 6V                                 |  |  |

- $\textbf{Note} \quad \textbf{1:} \quad \text{The minimum } V_{\text{IN}} \text{ must meet two conditions: } V_{\text{IN}} \geq 2.1V \text{ and } V_{\text{IN}} \geq V_{\text{OUT}(\text{MAX})} + V_{\text{DROPOUT}(\text{MAX})}.$

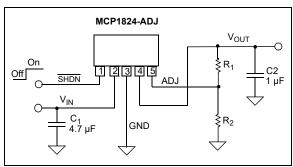

- V<sub>R</sub> is the nominal regulator output voltage for the fixed cases.  $V_R = 1.2V$ , 1.8V, etc.  $V_R$  is the desired set point output voltage for the adjustable cases.  $V_R = V_{ADJ} * ((R_1/R_2)+1)$ . Figure 4-1.

- 3: TCV<sub>OUT</sub> = (V<sub>OUT-HIGH</sub> V<sub>OUT-LOW</sub>) \*10<sup>6</sup> / (V<sub>R</sub> \* ΔTemperature). V<sub>OUT-HIGH</sub> is the highest voltage measured over the temperature range. V<sub>OUT-LOW</sub> is the lowest voltage measured over the temperature range.

- 4: Load regulation is measured at a constant junction temperature using low duty-cycle pulse testing. Load regulation is tested over a load range from 1 mA to the maximum specified output current.

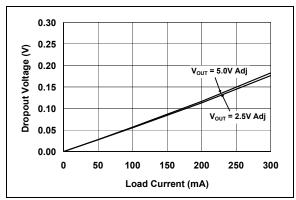

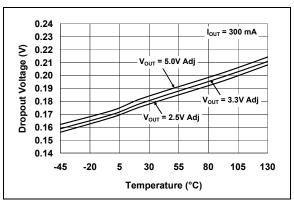

- 5: Dropout voltage is defined as the input-to-output voltage differential at which the output voltage drops 2% below its nominal value that was measured with an input voltage of V<sub>IN</sub> = V<sub>OUT(MAX)</sub> + V<sub>DROPOUT(MAX)</sub>.

- 6: The junction temperature is approximated by soaking the device under test at an ambient temperature equal to the desired junction temperature. The test time is small enough such that the rise in the junction temperature over the ambient temperature is not significant.

### AC/DC CHARACTERISTICS (CONTINUED)

**Electrical Specifications:** Unless otherwise noted,  $V_{IN} = V_{OUT(MAX)} + V_{DROPOUT(MAX)}$ , **Note 1**,  $V_R = 1.8V$  for Adjustable Output,  $I_{OUT} = 1$  mA,  $C_{IN} = C_{OUT} = 4.7 \mu F$  (X7R Ceramic),  $T_A = +25^{\circ}C$ .

Boldface type applies for junction temperatures, T<sub>J</sub> (Note 6) of -40°C to +125°C

| Boldlace type applies for juricuor  | Tomporataros, 1j                    |                       |                      | <u> </u>              |                   |                                                                                                                                                                                                 |  |  |  |

|-------------------------------------|-------------------------------------|-----------------------|----------------------|-----------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Parameters                          | Sym                                 | Min                   | Тур                  | Max                   | Units             | Conditions                                                                                                                                                                                      |  |  |  |

| Load Regulation                     | ΔV <sub>OUT</sub> /V <sub>OUT</sub> | -1.0                  | ±0.5                 | 1.0                   | %                 | I <sub>OUT</sub> = 1 mA to 300 mA,<br>(Note 4)                                                                                                                                                  |  |  |  |

| Output Short Circuit Current        | I <sub>OUT_SC</sub>                 | _                     | 720                  | _                     | mA                | R <sub>LOAD</sub> < 0.1Ω, Peak Current                                                                                                                                                          |  |  |  |

| Dropout Voltage                     | V <sub>DROPOUT</sub>                | _                     | 200                  | 320                   | mV                | Note 5, I <sub>OUT</sub> = 300 mA,<br>V <sub>IN(MIN)</sub> = 2.1V                                                                                                                               |  |  |  |

| Pulsed Applications                 |                                     |                       |                      |                       |                   |                                                                                                                                                                                                 |  |  |  |

| Maximum Pulsed Output<br>Current    | I <sub>PULSE</sub>                  | _                     | 500                  | _                     | mA                | $\begin{split} &V_{\text{IN}} = 2.1 \text{V to } 6.0 \text{V} \\ &V_{\text{R}} = 0.8 \text{V to } 5.0 \text{V}, \\ &\text{Duty Cycle} \leq 60\%, \\ &\text{Period} < 10 \text{ ms} \end{split}$ |  |  |  |

| Maximum Pulsed Output Duty<br>Cycle | PULSE_DUTY                          | _                     | _                    | 60                    | %                 | $V_{IN}$ = 2.1V to 6.0V,<br>$V_{R}$ = 0.8V to 5.0V,<br>$I_{OUT}$ = 500 mA,<br>Period < 10 ms                                                                                                    |  |  |  |

| Maximum Pulsed Output Period        | I <sub>PULSE_PERIOD</sub>           | _                     | _                    | 10                    | ms                | V <sub>IN</sub> = 2.1V to 6.0V<br>V <sub>R</sub> = 0.8V to 5.0V,<br>I <sub>OUT</sub> = 500 mA                                                                                                   |  |  |  |

| Adjust Pin Characteristics (Adj     | ustable Output O                    | nly)                  | _                    |                       |                   |                                                                                                                                                                                                 |  |  |  |

| Adjustable Output Voltage<br>Range  | $V_{OUT\_ADJ}$                      | 0.8                   | _                    | 5.5                   | >                 |                                                                                                                                                                                                 |  |  |  |

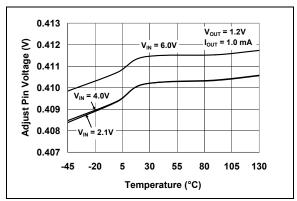

| Adjust Pin Reference Voltage        | $V_{ADJ}$                           | 0.402                 | 0.410                | 0.418                 | >                 | $V_{IN}$ = 2.1V to $V_{IN}$ = 6.0V, $I_{OUT}$ = 1 mA                                                                                                                                            |  |  |  |

| Adjust Pin Leakage Current          | I <sub>ADJ</sub>                    | -10                   | ±0.01                | +10                   | nA                | $V_{IN} = 6.0V$ , $V_{ADJ} = 0V$ to 6V                                                                                                                                                          |  |  |  |

| Adjust Temperature Coefficient      | TCV <sub>OUT</sub>                  | _                     | 40                   | _                     | ppm/°C            | Note 3                                                                                                                                                                                          |  |  |  |

| Fixed-Output Characteristics (F     | ixed Output Only                    | ·)                    |                      |                       |                   |                                                                                                                                                                                                 |  |  |  |

| Voltage Regulation                  | V <sub>OUT</sub>                    | V <sub>R</sub> - 2.5% | V <sub>R</sub> ±0.5% | V <sub>R</sub> + 2.5% | V                 | Note 2                                                                                                                                                                                          |  |  |  |

| Power Good Characteristics          |                                     |                       |                      |                       |                   |                                                                                                                                                                                                 |  |  |  |

| PWRGD Input Voltage Operat-         | $V_{PWRGD\_VIN}$                    | 1.0                   | _                    | 6.0                   | V                 | T <sub>A</sub> = +25°C                                                                                                                                                                          |  |  |  |

| ing Range                           |                                     | 1.2                   | _                    | 6.0                   |                   | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                                                                                                                                                  |  |  |  |

|                                     |                                     |                       |                      |                       |                   | For $V_{IN}$ < 2.1V, $I_{SINK}$ = 100 $\mu$ A                                                                                                                                                   |  |  |  |

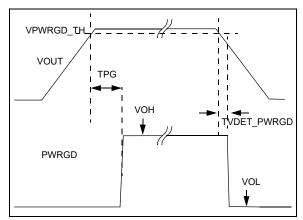

| PWRGD Threshold Voltage             | $V_{PWRGD\_TH}$                     |                       |                      |                       | %V <sub>OUT</sub> | Falling Edge                                                                                                                                                                                    |  |  |  |

| (Referenced to V <sub>OUT</sub> )   |                                     | 89                    | 92                   | 95                    |                   | V <sub>OUT</sub> < 2.5V Fixed,<br>V <sub>OUT</sub> = Adj.                                                                                                                                       |  |  |  |

|                                     |                                     | 90                    | 92                   | 94                    |                   | V <sub>OUT</sub> >= 2.5V Fixed                                                                                                                                                                  |  |  |  |

| PWRGD Threshold Hysteresis          | V <sub>PWRGD_HYS</sub>              | 1.0                   | 2.0                  | 3.0                   | %V <sub>OUT</sub> |                                                                                                                                                                                                 |  |  |  |

- $\textbf{Note} \quad \textbf{1:} \quad \text{The minimum } V_{\text{IN}} \text{ must meet two conditions: } V_{\text{IN}} \geq 2.1 V \text{ and } V_{\text{IN}} \geq V_{\text{OUT}(\text{MAX})} + V_{\text{DROPOUT}(\text{MAX})}.$

- 2:  $V_R$  is the nominal regulator output voltage for the fixed cases.  $V_R$  = 1.2V, 1.8V, etc.  $V_R$  is the desired set point output voltage for the adjustable cases.  $V_R$  =  $V_{ADJ} * ((R_1/R_2)+1)$ . Figure 4-1.

- 3: TCV<sub>OUT</sub> = (V<sub>OUT-HIGH</sub> V<sub>OUT-LOW</sub>) \*10<sup>6</sup> / (V<sub>R</sub> \* ΔTemperature). V<sub>OUT-HIGH</sub> is the highest voltage measured over the temperature range. V<sub>OUT-LOW</sub> is the lowest voltage measured over the temperature range.

- 4: Load regulation is measured at a constant junction temperature using low duty-cycle pulse testing. Load regulation is tested over a load range from 1 mA to the maximum specified output current.

- 5: Dropout voltage is defined as the input-to-output voltage differential at which the output voltage drops 2% below its nominal value that was measured with an input voltage of V<sub>IN</sub> = V<sub>OUT(MAX)</sub> + V<sub>DROPOUT(MAX)</sub>.

- 6: The junction temperature is approximated by soaking the device under test at an ambient temperature equal to the desired junction temperature. The test time is small enough such that the rise in the junction temperature over the ambient temperature is not significant.

# AC/DC CHARACTERISTICS (CONTINUED)

**Electrical Specifications:** Unless otherwise noted,  $V_{IN} = V_{OUT(MAX)} + V_{DROPOUT(MAX)}$ , **Note 1**,  $V_R = 1.8V$  for Adjustable Output,  $I_{OUT}$  = 1 mA,  $C_{IN}$  =  $C_{OUT}$  = 4.7  $\mu F$  (X7R Ceramic),  $T_A$  = +25  $^{\circ}C_{IN}$

Boldface type applies for junction temperatures, T<sub>J</sub> (Note 6) of -40°C to +125°C

| Parameters                                     | Sym                     | Min  | Тур    | Max  | Units            | Conditions                                                                                                        |

|------------------------------------------------|-------------------------|------|--------|------|------------------|-------------------------------------------------------------------------------------------------------------------|

| PWRGD Output Voltage Low                       | $V_{PWRGD\_L}$          |      | 0.05   | 0.4  | V                | I <sub>PWRGD SINK</sub> = 1.2 mA,<br>ADJ = 0V                                                                     |

| PWRGD Output Current Sink Capability           | I <sub>PWRGD</sub>      | 1.2  | 6.0    | _    | mA               | V <sub>PWRGD</sub> = 0.200V                                                                                       |

| PWRGD Leakage                                  | P <sub>WRGD_LK</sub>    | _    | 1      | _    | nA               | $V_{PWRGD} = V_{IN} = 6.0V$                                                                                       |

| PWRGD Time Delay                               | T <sub>PG</sub>         | _    | 110    | _    | μs               | Rising Edge $R_{PULLUP} = 10 \text{ k}\Omega$                                                                     |

| Detect Threshold to PWRGD<br>Active Time Delay | T <sub>VDET-PWRGD</sub> | ı    | 200    | _    | μs               | $V_{OUT} = V_{PWRGD\_TH} + 50 \text{ mV}$<br>to $V_{PWRGD\_TH} - 50 \text{ mV}$                                   |

| Shutdown Input                                 |                         |      |        |      |                  |                                                                                                                   |

| Logic High Input                               | V <sub>SHDN-HIGH</sub>  | 45   | _      | _    | %V <sub>IN</sub> | V <sub>IN</sub> = 2.1V to 6.0V                                                                                    |

| Logic Low Input                                | V <sub>SHDN-LOW</sub>   | _    | _      | 15   | %V <sub>IN</sub> | V <sub>IN</sub> = 2.1V to 6.0V                                                                                    |

| SHDN Input Leakage Current                     | SHDN <sub>ILK</sub>     | -0.1 | ±0.001 | +0.1 | μA               | V <sub>IN</sub> = 6V, SHDN =V <sub>IN</sub> ,<br>SHDN = GND                                                       |

| AC Performance                                 |                         |      |        |      |                  |                                                                                                                   |

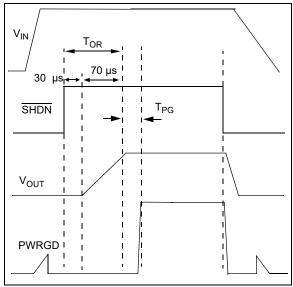

| Output Delay From SHDN                         | T <sub>OR</sub>         | _    | 100    | _    | μs               | SHDN = GND to V <sub>IN</sub> ,<br>V <sub>OUT</sub> = GND to 95% V <sub>R</sub>                                   |

| Output Noise                                   | e <sub>N</sub>          | _    | 2.0    | _    | μV/√Hz           | $I_{OUT}$ = 200 mA, f = 1 kHz,<br>$C_{OUT}$ = 10 $\mu$ F (X7R Ceramic),<br>$V_{OUT}$ = 2.5V                       |

| Power Supply Ripple Rejection<br>Ratio         | PSRR                    | _    | 55     | _    | dB               | $\begin{split} &f=100~Hz,\\ &I_{OUT}=10~mA,\\ &V_{INAC}=200~mV~pk\text{-}pk,\\ &C_{IN}=0~\mu\text{F} \end{split}$ |

| Thermal Shutdown Temperature                   | T <sub>SD</sub>         | _    | 150    | _    | °C               | I <sub>OUT</sub> = 100 μA, V <sub>OUT</sub> = 1.8V,<br>V <sub>IN</sub> = 2.8V                                     |

| Thermal Shutdown Hysteresis                    | $\Delta T_{\sf SD}$     | _    | 10     | _    | °C               | I <sub>OUT</sub> = 100 μA, V <sub>OUT</sub> = 1.8V,<br>V <sub>IN</sub> = 2.8V                                     |

Note 1: The minimum  $V_{IN}$  must meet two conditions:  $V_{IN} \ge 2.1V$  and  $V_{IN} \ge V_{OUT(MAX)} + V_{DROPOUT(MAX)}$ .

- $V_R$  is the nominal regulator output voltage for the fixed cases.  $V_R = 1.2V$ , 1.8V, etc.  $V_R$  is the desired set point output voltage for the adjustable cases.  $V_R = V_{ADJ} * ((R_1/R_2)+1)$ . Figure 4-1.  $TCV_{OUT} = (V_{OUT-HIGH} - V_{OUT-LOW}) *10^6 / (V_R * \Delta Temperature)$ .  $V_{OUT-HIGH}$  is the highest voltage measured over the

- temperature range.  $V_{\mbox{\scriptsize OUT-LOW}}$  is the lowest voltage measured over the temperature range.

- 4: Load regulation is measured at a constant junction temperature using low duty-cycle pulse testing. Load regulation is tested over a load range from 1 mA to the maximum specified output current.

- Dropout voltage is defined as the input-to-output voltage differential at which the output voltage drops 2% below its nominal value that was measured with an input voltage of  $V_{IN} = V_{OUT(MAX)} + V_{DROPOUT(MAX)}$

- The junction temperature is approximated by soaking the device under test at an ambient temperature equal to the desired junction temperature. The test time is small enough such that the rise in the junction temperature over the ambient temperature is not significant.

# **TEMPERATURE SPECIFICATIONS**

| Parameters                           | Sym               | Min | Тур | Max  | Units | Conditions             |  |

|--------------------------------------|-------------------|-----|-----|------|-------|------------------------|--|

| Temperature Ranges                   |                   |     |     |      |       |                        |  |

| Operating Junction Temperature Range | $T_J$             | -40 | _   | +125 | °C    | Steady State           |  |

| Maximum Junction Temperature         | $T_J$             | _   | _   | +150 | °C    | Transient              |  |

| Storage Temperature Range            | T <sub>A</sub>    | -65 | _   | +150 | °C    |                        |  |

| Thermal Package Resistances          |                   |     |     |      |       |                        |  |

| Thermal Resistance, 3LD SOT-223      | $\theta_{JA}$     | _   | 62  | _    | °C/W  | EIA/JEDEC JESD51-751-7 |  |

|                                      | $\theta_{\sf JC}$ | _   | 15  | _    |       | 4 Layer Board          |  |

| Thermal Resistance, 5LD SOT-23       | $\theta_{JA}$     | _   | 256 | _    | °C/W  | EIA/JEDEC JESD51-751-7 |  |

|                                      | $\theta_{\sf JC}$ | _   | 81  | _    |       | 4 Layer Board          |  |

| Thermal Resistance, 5LD SOT-223      | $\theta_{JA}$     | _   | 62  | _    | °C/W  | EIA/JEDEC JESD51-751-7 |  |

|                                      | $\theta_{\sf JC}$ | _   | 15  | _    |       | 4 Layer Board          |  |

#### 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

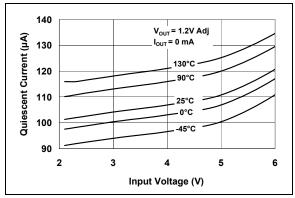

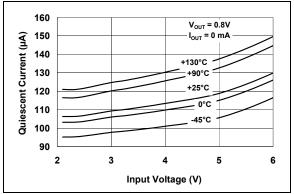

**FIGURE 2-1:** Quiescent Current vs. Input Voltage (Adjustable Version).

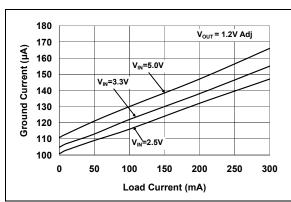

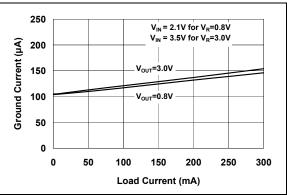

**FIGURE 2-2:** Ground Current vs. Load Current (Adjustable Version).

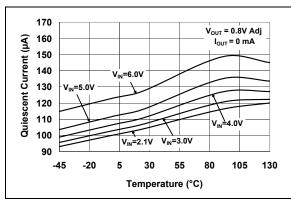

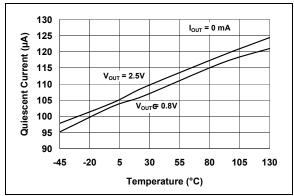

**FIGURE 2-3:** Quiescent Current vs. Junction Temperature (Adjustable Version).

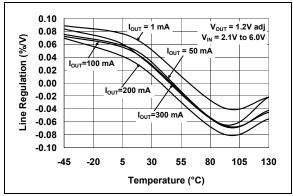

**FIGURE 2-4:** Line Regulation vs. Temperature (Adjustable Version).

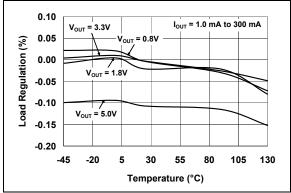

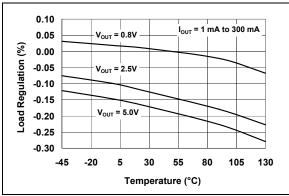

FIGURE 2-5: Load Regulation vs. Temperature (Adjustable Version).

**FIGURE 2-6:** Adjust Pin Voltage vs. Temperature (Adjustable Version).

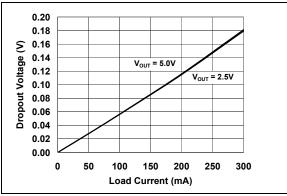

FIGURE 2-7: Dropout Voltage vs. Load Current (Adjustable Version).

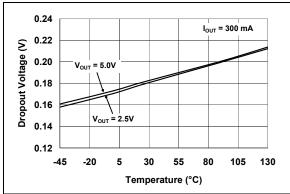

**FIGURE 2-8:** Dropout Voltage vs. Temperature (Adjustable Version).

**FIGURE 2-9:** Power Good (PWRGD) Time Delay vs. Temperature.

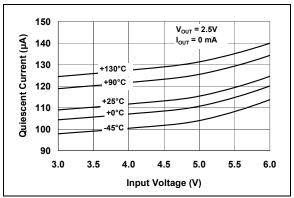

**FIGURE 2-10:** Quiescent Current vs. Input Voltage.

**FIGURE 2-11:** Quiescent Current vs. Input Voltage.

FIGURE 2-12: Ground Current vs. Load Current.

**FIGURE 2-13:** Quiescent Current vs. Temperature.

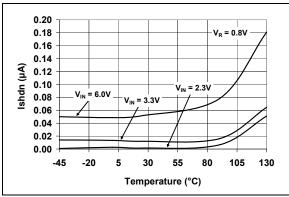

FIGURE 2-14: I<sub>SHDN</sub> vs. Temperature.

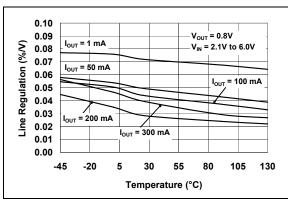

**FIGURE 2-15:** Line Regulation vs. Temperature.

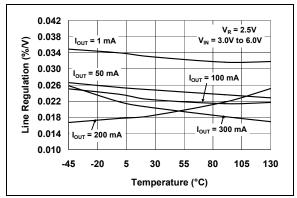

**FIGURE 2-16:** Line Regulation vs. Temperature.

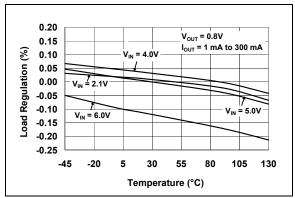

**FIGURE 2-17:** Load Regulation vs. Temperature.

**FIGURE 2-18:** Load Regulation vs. Temperature.

FIGURE 2-19: Dropout Voltage vs. Load Current.

FIGURE 2-20: Dropout Voltage vs. Temperature.

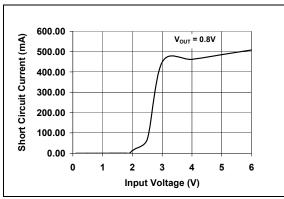

FIGURE 2-21: Short Circuit Current vs. Input Voltage.

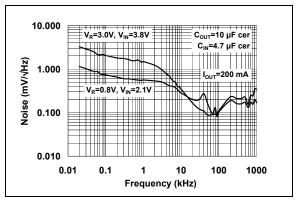

**FIGURE 2-22:** Output Noise Voltage Density vs. Frequency.

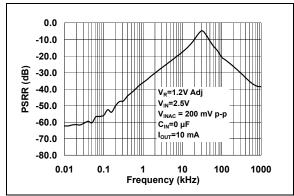

FIGURE 2-23: Power Supply Ripple Rejection (PSRR) vs. Frequency (Adj.).

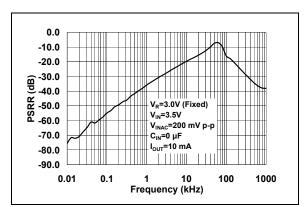

FIGURE 2-24: Power Supply Ripple Rejection (PSRR) vs. Frequency.

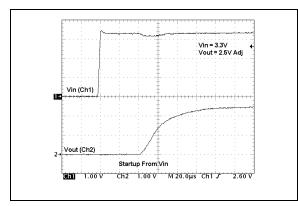

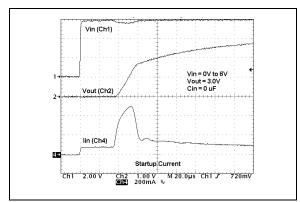

**FIGURE 2-25:** Startup from  $V_{IN}$  (Adjustable Version).

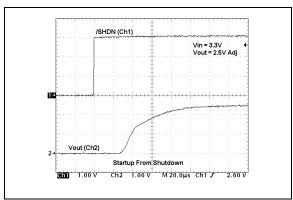

**FIGURE 2-26:** Startup from Shutdown (Adjustable Version).

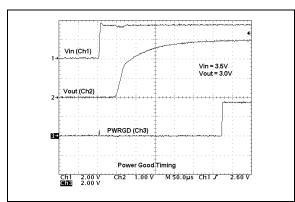

FIGURE 2-27: Power Good (PWRGD) Timing.

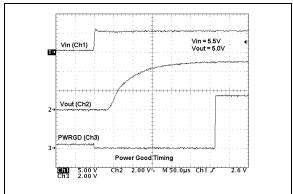

FIGURE 2-28: Power Good (PWRGD)

Timing.

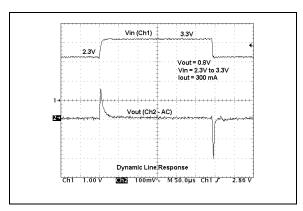

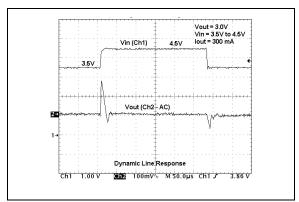

FIGURE 2-29: Dynamic Line Response.

FIGURE 2-30: Dynamic Line Response.

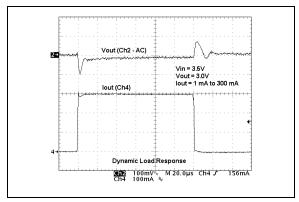

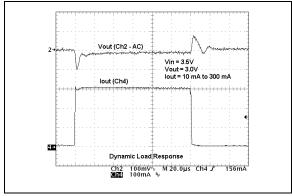

FIGURE 2-31: Dynamic Load Response.

FIGURE 2-32: Dynamic Load Response.

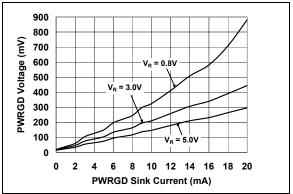

**FIGURE 2-33:** Power Good Pulldown Voltage Vs Load.

FIGURE 2-34: Startup Current.

#### 3.0 PIN DESCRIPTION

The descriptions of the pins are listed in Table 3-1.

TABLE 3-1: PIN FUNCTION TABLE

|                | SOT-223        |                | so             | Γ-23         |                  |                                               |

|----------------|----------------|----------------|----------------|--------------|------------------|-----------------------------------------------|

| 3-Pin<br>Fixed | 5-Pin<br>Fixed | 5-Pin<br>Adj   | 5-Pin<br>Fixed | 5-Pin<br>Adj | Name             | Description                                   |

| _              | 1              | 1              | 3              | 3            | SHDN             | Shutdown Control Input (active-low)           |

| 1              | 2              | 2              | 1              | 1            | V <sub>IN</sub>  | Input Voltage Supply                          |

| 2              | 3              | 3              | 2              | 2            | GND              | Ground                                        |

| 3              | 4              | 4              | 5              | 5            | V <sub>OUT</sub> | Regulated Output Voltage                      |

| _              | 5              | _              | 4              | _            | PWRGD            | Power Good Output                             |

| _              | _              | 5              | _              | 4            | ADJ              | Output Voltage Adjust/Sense Input             |

| Exposed<br>Pad | Exposed<br>Pad | Exposed<br>Pad | _              | _            | EP               | Exposed Pad of the Package (ground potential) |

# 3.1 Shutdown Control Input (SHDN)

The  $\overline{SHDN}$  input is used to turn the LDO output voltage on and off. When the  $\overline{SHDN}$  input is at a logic-high level, the LDO output voltage is enabled. When the  $\overline{SHDN}$  input is pulled to a logic-low level, the LDO output voltage is disabled. When the  $\overline{SHDN}$  input is pulled low, the PWRGD output also goes low and the LDO enters a low quiescent current shutdown state where the typical quiescent current is 0.1  $\mu$ A.

# 3.2 Input Voltage Supply (V<sub>IN</sub>)

Connect the unregulated or regulated input voltage source to  $V_{\text{IN}}.$  If the input voltage source is located several inches away from the LDO, or the input source is a battery, it is recommended that an input capacitor be used. A typical input capacitance value of 1  $\mu F$  to 10  $\mu F$  should be sufficient for most applications. The type of capacitor used can be ceramic, tantalum, or aluminum electrolytic. The low ESR characteristics of the ceramic capacitor will yield better noise and PSRR performance at high frequency.

### 3.3 Ground (GND)

For the optimal Noise and Power Supply Rejection Ratio (PSRR) performance, the GND pin of the LDO should be tied to an electrically quiet circuit ground. This will help the LDO power supply rejection ratio and noise performance. The ground pin of the LDO only conducts the ground current of the LDO, so a heavy trace is not required. For applications that have switching or noisy inputs, tie the GND pin to the return of the output capacitor. Ground planes help lower inductance and voltage spikes caused by fast transient load currents and are recommended for applications that are subjected to fast load transients.

# 3.4 Regulated Output Voltage (V<sub>OUT</sub>)

The  $V_{OUT}$  pin is the regulated output voltage of the LDO. A minimum output capacitance of 1.0 µF is required for LDO stability. The MCP1824/MCP1824S is stable with ceramic, tantalum, and aluminum-electrolytic capacitors. See **Section 4.3 "Output Capacitor"** for output capacitor selection guidance.

### 3.5 Power Good Output (PWRGD)

For fixed applications, the PWRGD output is an opendrain output used to indicate when the LDO output voltage is within 92% (typically) of its nominal regulation value. The PWRGD threshold has a typical hysteresis value of 2%. The PWRGD output is delayed by 110  $\mu s$  (typical) from the time the LDO output is within 92% + 3% (maximum hysteresis) of the regulated output value on power-up. This delay time is internally fixed.

#### 3.6 Output Voltage Adjust Input (ADJ)

For adjustable applications, the output voltage is connected to the ADJ input through a resistor divider that sets the output voltage regulation value. This provides the users the capability to set the output voltage to any value they desire within the 0.8V to 5.0V range of the device.

#### 3.7 Exposed Pad (EP)

The SOT-223 package has an exposed metal pad on the bottom of the package. The exposed metal pad gives the device better thermal characteristics by providing a good thermal path to either the PCB or heatsink to remove heat from the device. The exposed pad of the package is at ground potential.

### 4.0 DEVICE OVERVIEW

The MCP1824/MCP1824S is a 300 mA output current, Low Dropout (LDO) voltage regulator. The low dropout voltage of 200 mV typical at 300 mA of current makes it ideal for battery-powered applications. The input voltage range is 2.1V to 6.0V. Unlike other high output current LDOs, the MCP1824/MCP1824S only draws a maximum of 220  $\mu$ A of quiescent current. The MCP1824 adds a shutdown control input pin and a power good output pin. The two output voltage options are fixed or adjustable. The adjustable output voltage is set using two external resistors.

### 4.1 LDO Output Voltage

The MCP1824 LDO is available with either a fixed output voltage or an adjustable output voltage. The output voltage range is 0.8V to 5.0V for either version. The MCP1824S LDO is available as a fixed voltage device.

#### 4.1.1 ADJUST INPUT

The adjustable version of the MCP1824 uses the ADJ pin to get the output voltage feedback for output voltage regulation. This allows the user to set the output voltage of the device with two external resistors. The nominal voltage for ADJ is 0.41V.

Figure 4-1 shows the adjustable version of the MCP1824. Resistors  $R_1$  and  $R_2$  form the resistor divider network necessary to set the output voltage. With this configuration, Equation 4-1 represents the equation for setting  $V_{OLIT}$ .

### **EQUATION 4-1: CALCULATING VOUT**

$$V_{OUT} = V_{ADJ} \left( \frac{R_1 + R_2}{R_2} \right)$$

Where:

$V_{OUT}$  = LDO Output Voltage  $V_{ADJ}$  = ADJ Pin Voltage (typically 0.41V)

**FIGURE 4-1:** Typical Adjustable Output Voltage Application Circuit.

The allowable resistance value range for resistor R $_2$  is from 10 k $\Omega$  to 200 k $\Omega$ . Solving Equation 4-1 for R $_1$  yields Equation 4-2.

# EQUATION 4-2: CALCULATING ADJ PIN RESISTOR VALUES

$R_1 = R_2 \! \left( \! \frac{V_{OUT}}{V_{ADJ}} \! - I \! \right) \label{eq:reconstruction}$  Where:

V<sub>OUT</sub> = LDO Output Voltage V<sub>ADJ</sub> = ADJ Pin Voltage (typically 0.41V)

# 4.2 Output Current and Current Limiting

The MCP1824/MCP1824S LDO is tested and ensured to supply a minimum of 300 mA of output current. The MCP1824/MCP1824S has no minimum output load, so the output load current can go to 0 mA and the LDO will continue to regulate the output voltage to within tolerance.

The MCP1824/MCP1824S also incorporates an output current limit. If the output voltage falls below 0.7V due to an overload condition (usually represents a shorted load condition), the output current is limited to 720 mA (typical). If the overload condition is a soft overload, the MCP1824/MCP1824S will supply higher load currents of up to 900 mA. The MCP1824/MCP1824S should not be operated in this condition continuously as it may result in failure of the device. However, this does allow for device usage in applications that have higher pulsed load currents having an average output current value of 300 mA or less.

Output overload conditions may also result in an overtemperature shutdown of the device. If the junction temperature rises above 150°C (typical), the LDO will shut down the output voltage. See **Section 4.8 "Overtemperature Protection"** for more information on overtemperature shutdown.

#### 4.3 Output Capacitor

The MCP1824/MCP1824S requires a minimum output capacitance of 1  $\mu$ F for output voltage stability. Ceramic capacitors are recommended because of their size, cost, and environmental robustness qualities.

Aluminum-electrolytic and tantalum capacitors can be used on the LDO output as well. The Equivalent Series Resistance (ESR) of the electrolytic output capacitor must be no greater than 1 ohm. The output capacitor should be located as close to the LDO output as is practical. Ceramic materials X7R and X5R have low temperature coefficients and are well within the acceptable ESR range required. A typical 1  $\mu F$  X7R 0805 capacitor has an ESR of 50 milli-ohms.

Larger LDO output capacitors can be used with the MCP1824/MCP1824S to improve dynamic performance and power supply ripple rejection performance. A maximum of 22  $\mu$ F is recommended. Aluminum-electrolytic capacitors are not recommended for low temperature applications of <  $-25^{\circ}$ C.

### 4.4 Input Capacitor

Low input source impedance is necessary for the LDO output to operate properly. When operating from batteries, or in applications with long lead length (> 10 inches) between the input source and the LDO, some input capacitance is recommended. A minimum of 1.0  $\mu F$  to 4.7  $\mu F$  is recommended for most applications.

For applications that have output step load requirements, the input capacitance of the LDO is very important. The input capacitance provides the LDO with a good local low-impedance source to pull the transient currents from, in order to respond quickly to the output load step. For good step response performance, the input capacitor should be of equivalent (or higher) value than the output capacitor. The capacitor should be placed as close to the input of the LDO as is practical. Larger input capacitors will also help reduce any high-frequency noise on the input and output of the LDO and reduce the effects of any inductance that exists between the input source voltage and the input capacitance of the LDO.

#### 4.5 Power Good Output (PWRGD)

The PWRGD output is used to indicate when the output voltage of the LDO is within 92% (typical value, see **Section 1.0 "Electrical Characteristics"** for Minimum and Maximum specifications) of its nominal regulation value.

As the output voltage of the LDO rises, the PWRGD output will be held low until the output voltage has exceeded the power good threshold plus the hysteresis value. Once this threshold has been exceeded, the power good time delay is started (shown as  $T_{PG}$  in the Electrical Characteristics table). The power good time

delay is fixed at 110 µs (typical). After the time delay period, the PWRGD output will go high, indicating that the output voltage is stable and within regulation limits.

If the output voltage of the LDO falls below the power good threshold, the power good output will transition low. The power good circuitry has a 200 µs delay when detecting a falling output voltage, which helps to increase noise immunity of the power good output and avoid false triggering of the power good output during fast output transients. See Figure 4-2 for power good timing characteristics.

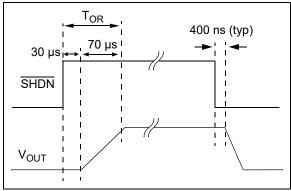

When the LDO is put into Shutdown mode using the SHDN input, the power good output is pulled low immediately, indicating that the output voltage will be out of regulation. The timing diagram for the power good output when using the shutdown input is shown in Figure 4-3.

The power good output is an open-drain output that can be pulled up to any voltage that is equal to or less than the LDO input voltage. This output is capable of sinking 1.2 mA minimum ( $V_{PWRGD} < 0.4V$  maximum).

FIGURE 4-2: Power Good Timing.

**FIGURE 4-3:** Power Good Timing from Shutdown.

# 4.6 Shutdown Input (SHDN)

The  $\overline{SHDN}$  input is an active-low input signal that turns the LDO on and off. The  $\overline{SHDN}$  threshold is a percentage of the input voltage. The typical value of this shutdown threshold is 30% of  $V_{IN}$ , with minimum and maximum limits over the entire operating temperature range of 45% and 15%, respectively.

The SHDN input will ignore low-going pulses (pulses meant to shut down the LDO) that are up to 400 ns in pulse width. If the shutdown input is pulled low for more than 400 ns, the LDO will enter Shutdown mode. This small bit of filtering helps to reject any system noise spikes on the shutdown input signal.

On the rising edge of the  $\overline{SHDN}$  input, the shutdown circuitry has a 30 µs delay before allowing the LDO output to turn on. This delay helps to reject any false turn-on signals or noise on the  $\overline{SHDN}$  input signal. After the 30 µs delay, the LDO output enters its soft-start period as it rises from 0V to its final regulation value. If the  $\overline{SHDN}$  input signal is pulled low during the 30 µs delay period, the timer will be reset and the delay time will start over again on the next rising edge of the  $\overline{SHDN}$  input. The total time from the  $\overline{SHDN}$  input going high (turn-on) to the LDO output being in regulation is typically 100 µs. See Figure 4-4 for a timing diagram of the  $\overline{SHDN}$  input.

FIGURE 4-4:

Shutdown Input Timing

# 4.7 Dropout Voltage and Undervoltage Lockout

Dropout voltage is defined as the input-to-output voltage differential at which the output voltage drops 2% below the nominal value that was measured with a  $V_R$  + 0.5V differential applied. The MCP1824/ MCP1824S LDO has a very low dropout voltage specification of 210 mV (typical) at 300 mA of output current. See  $Section\ 1.0\ "Electrical\ Characteristics"$  for maximum dropout voltage specifications.

The MCP1824/MCP1824S LDO operates across an input voltage range of 2.1V to 6.0V and incorporates input Undervoltage Lockout (UVLO) circuitry that keeps the LDO output voltage off until the input voltage reaches a minimum of 2.00V (typical) on the rising edge of the input voltage. As the input voltage falls, the LDO output will remain on until the input voltage level reaches 1.82V (typical).

Since the MCP1824/MCP1824S LDO undervoltage lockout activates at 1.82V as the input voltage is falling, the dropout voltage specification does not apply for output voltages that are less than 1.8V.

For high-current applications, voltage drops across the PCB traces must be taken into account. The trace resistances can cause significant voltage drops between the input voltage source and the LDO. For applications with input voltages near 2.1V, these PCB trace voltage drops can sometimes lower the input voltage enough to trigger a shutdown due to undervoltage lockout.

### 4.8 Overtemperature Protection

The MCP1824/MCP1824S LDO has temperature sensing circuitry to prevent the junction temperature from exceeding approximately 150°C. If the LDO junction temperature does reach 150°C, the LDO output will be turned off until the junction temperature cools to approximately 140°C, at which point the LDO output will automatically resume normal operation. If the internal power dissipation continues to be excessive, the device will again shut off. The junction temperature of the die is a function of power dissipation, ambient temperature and package thermal resistance. See **Section 5.0 "Application Circuits/Issues"** for more information on LDO power dissipation and junction temperature.

#### 5.0 APPLICATION CIRCUITS/ **ISSUES**

#### 5.1 **Typical Application**

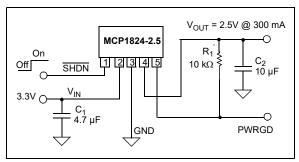

The MCP1824/MCP1824S is used for applications that require high LDO output current and a power good output.

FIGURE 5-1: Typical Application Circuit.

#### 5.1.1 APPLICATION CONDITIONS

Package Type SOT-223-5 Input Voltage Range  $3.3V \pm 5\%$ V<sub>IN</sub> maximum 3.465V V<sub>IN</sub> minimum 3.135V

> 0.350V V<sub>DROPOUT (max)</sub> V<sub>OUT</sub> (typical) 2.5V

> > 300 mA maximum I<sub>OUT</sub>

0.240W P<sub>DISS</sub> (typical) Temperature Rise 14.88°C

#### 5.2 **Power Calculations**

#### 5.2.1 POWER DISSIPATION

The internal power dissipation within the MCP1824/ MCP1824S is a function of input voltage, output voltage, output current and quiescent current. Equation 5-1 can be used to calculate the internal power dissipation for the LDO.

#### **EQUATION 5-1:**

$P_{LDO} = (V_{IN(MAX)}) - V_{OUT(MIN)}) \times I_{OUT(MAX)}$

Where:

P<sub>LDO</sub> = LDO Pass device internal

power dissipation

$V_{IN(MAX)}$  = Maximum input voltage

V<sub>OUT(MIN)</sub> = LDO minimum output voltage

In addition to the LDO pass element power dissipation, there is power dissipation within the MCP1824/ MCP1824S as a result of quiescent or ground current. The power dissipation as a result of the ground current can be calculated using the following equation:

#### **EQUATION 5-2:**

$P_{I(GND)} = V_{IN(MAX)} \times I_{VIN}$ Where:

> $P_{I(GND)}$  = Power dissipation due to the quiescent current of the LDO

V<sub>IN(MAX)</sub> = Maximum input voltage

Current flowing in the V<sub>IN</sub> pin  $I_{VIN}$ with no LDO output current

(LDO quiescent current)

The total power dissipated within the MCP1824/ MCP1824S is the sum of the power dissipated in the LDO pass device and the P(I<sub>GND</sub>) term. Because of the CMOS construction, the typical I<sub>GND</sub> for the MCP1824/ MCP1824S is 120  $\mu$ A. Operating at a maximum  $V_{IN}$  of 3.465V results in a power dissipation of 0.12 milli-Watts for a 2.5V output. For most applications, this is small compared to the LDO pass device power dissipation and can be neglected.

maximum continuous operating junction temperature specified for the MCP1824/MCP1824S is +125°C. To estimate the internal junction temperature of the MCP1824/MCP1824S, the total internal power dissipation is multiplied by the thermal resistance from junction to ambient ( $R\theta_{JA}$ ) of the device. The thermal resistance from junction to ambient for the SOT-223-5 package is estimated at 62° C/W.

#### **EQUATION 5-3:**

$T_{J(MAX)} = P_{TOTAL} \times R\theta_{JA} + T_{AMAX}$

$T_{J(MAX)}$  = Maximum continuous junction temperature

P<sub>TOTAL</sub> = Total device power dissipation

$R\theta_{JA}$  = Thermal resistance from junction to

ambient

T<sub>AMAX</sub> = Maximum ambient temperature

The maximum power dissipation capability for a package can be calculated given the junction-to-ambient thermal resistance and the maximum ambient temperature for the application. Equation 5-4 can be used to determine the package maximum internal power dissipation.

#### **EQUATION 5-4:**

$$P_{D(MAX)} = \frac{(T_{J(MAX)} - T_{A(MAX)})}{R\theta_{JA}}$$

P<sub>D(MAX)</sub> = Maximum device power dissipation

$T_{J(MAX)}$  = maximum continuous junction

temperature

$T_{A(MAX)}$  = maximum ambient temperature

$R\theta_{JA}$  = Thermal resistance from junction-to-

ambient

#### **EQUATION 5-5:**

$$T_{J(RISE)} = P_{D(MAX)} \times R\theta_{JA}$$

T<sub>J(RISE)</sub> = Rise in device junction temperature over the ambient temperature

P<sub>D(MAX)</sub> = Maximum device power dissipation

$R\theta_{JA}$  = Thermal resistance from junction-to-

ambient

#### **EQUATION 5-6:**

$$T_J = T_{J(RISE)} + T_A$$

$T_{\perp}$  = Junction temperature

T<sub>J(RISE)</sub> = Rise in device junction temperature over the ambient temperature

$T_A$  = Ambient temperature

### 5.3 Typical Application

Internal power dissipation, junction temperature rise, junction temperature, and maximum power dissipation is calculated in the following example. The power dissipation as a result of ground current is small enough to be neglected.

#### 5.3.1 POWER DISSIPATION EXAMPLE

#### **Package**

Package Type = SOT-223-5

Input Voltage

$V_{IN} = 3.3V \pm 5\%$

#### **LDO Output Voltage and Current**

$V_{OUT} = 2.5V$

$I_{OLIT} = 300 \text{ mA}$

#### **Maximum Ambient Temperature**

$T_{A(MAX)} = 60^{\circ}C$

#### **Internal Power Dissipation**

$P_{LDO(MAX)} = (V_{IN(MAX)} - V_{OUT(MIN)}) \times I_{OUT(MAX)}$  $P_{LDO} = ((3.3V \times 1.05) - (2.5V \times 0.975))$

x 300 mA

$P_{LDO} = 0.308 \text{ Watts}$

#### 5.3.1.1 Device Junction Temperature Rise

The internal junction temperature rise is a function of internal power dissipation and the thermal resistance from junction-to-ambient for the application. The thermal resistance from junction-to-ambient (R $\theta_{JA}$ ) is derived from EIA/JEDEC standards for measuring thermal resistance. The EIA/JEDEC specification is JESD51. The standard describes the test method and board specifications for measuring the thermal resistance from junction to ambient. The actual thermal resistance for a particular application can vary depending on many factors such as copper area and thickness. Refer to AN792, "A Method to Determine How Much Power a SOT23 Can Dissipate in an Application" (DS00792), for more information regarding this subject.

$T_{J(RISE)} = P_{TOTAL} x R\theta_{JA}$

$T_{JRISE} = 0.308 \text{ W x } 62^{\circ} \text{ C/W}$

$T_{JRISE} = 19.1$ °C

### 5.3.1.2 Junction Temperature Estimate

To estimate the internal junction temperature, the calculated temperature rise is added to the ambient or offset temperature. For this example, the worst-case junction temperature is estimated below:

$$T_J = T_{JRISE} + T_{A(MAX)}$$

$T_J = 19.1^{\circ}C + 60.0^{\circ}C$

$T_J = 79.1^{\circ}C$

# 5.3.1.3 Maximum Package Power Dissipation at 60°C Ambient Temperature

# SOT-223-5 (62°C/W $R\theta_{JA}$ ):

$$P_{D(MAX)} = (125^{\circ}C - 60^{\circ}C) / 62^{\circ}C/W$$

$P_{D(MAX)} = 1.048W$

### SOT-23-5 (256°C/Watt Rθ ΙΔ):

$$P_{D(MAX)} = (125^{\circ}C - 60^{\circ}C)/256^{\circ}C/W$$

$P_{D(MAX)} = 0.254W$

From this table, you can see the difference in maximum allowable power dissipation between the SOT-223-5 package and the SOT-23-5 package.

#### 6.0 PACKAGING INFORMATION

#### 6.1 **Package Marking Information**

#### 5-Lead SOT-23 (MCP1824)

| Part Number (SOT-23, 5L) | Code |

|--------------------------|------|

| MCP1824T-0802E/OT        | UL   |

| MCP1824T-1202E/OT(VAO)   | UM   |

| MCP1824T-1802E/OT        | UP   |

| MCP1824T-2502E/OT        | UQ   |

| MCP1824T-2802E/OT        | 2M   |

| MCP1824T-3002E/OT        | UR   |

| MCP1824T-3302E/OT        | US   |

| MCP1824T-5002E/OT        | UT   |

| MCP1824T-ADJE/OT(VAO)    | UK   |

|                          |      |

#### Example:

#### 5-Lead SOT-223 (MCP1824)

#### Example:

### 3-Lead SOT-223 (MCP1824S)

#### Example:

Legend: XX...X Customer-specific information Year code (last digit of calendar year) Year code (last 2 digits of calendar year) YY WW Week code (week of January 1 is week '01') NNN Alphanumeric traceability code

(e3) Pb-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (e3) can be found on the outer packaging for this package.

Note: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

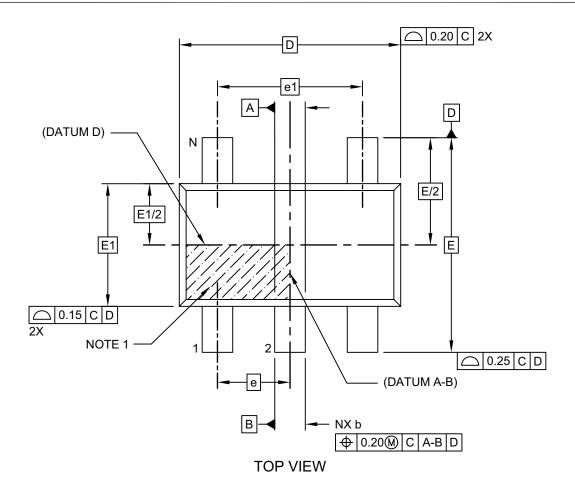

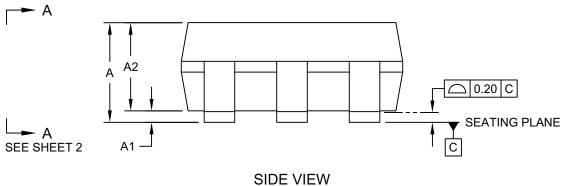

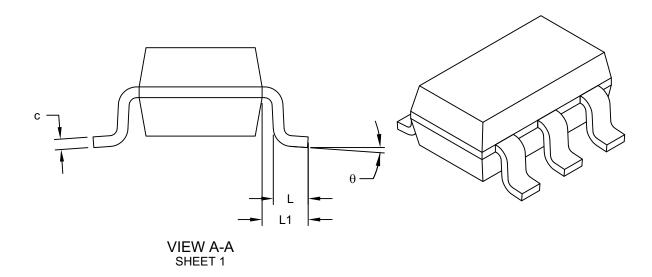

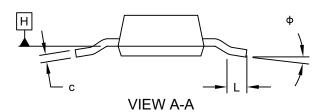

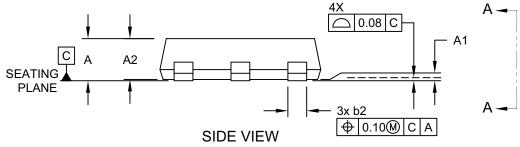

# 5-Lead Plastic Small Outline Transistor (OT) [SOT-23]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-091-OT Rev H Sheet 1 of 2

# 5-Lead Plastic Small Outline Transistor (OT) [SOT-23]

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |             |          |      |  |

|--------------------------|-------------|-------------|----------|------|--|

| Dimension                | MIN         | NOM         | MAX      |      |  |

| Number of Pins           | N           |             | 5        |      |  |

| Pitch                    | е           |             | 0.95 BSC |      |  |

| Outside lead pitch       | e1          |             | 1.90 BSC |      |  |

| Overall Height           | Α           | 0.90 - 1.45 |          |      |  |

| Molded Package Thickness | A2          | 0.89        | ı        | 1.30 |  |

| Standoff                 | A1          | -           | -        | 0.15 |  |

| Overall Width            | Е           | 2.80 BSC    |          |      |  |

| Molded Package Width     | E1          |             | 1.60 BSC |      |  |

| Overall Length           | D           |             | 2.90 BSC |      |  |

| Foot Length              | L           | 0.30        | ı        | 0.60 |  |

| Footprint                | L1          | 0.60 REF    |          |      |  |

| Foot Angle               | θ           | 0°          | -        | 10°  |  |

| Lead Thickness           | С           | 0.08        | -        | 0.26 |  |

| Lead Width               | b           | 0.20        | -        | 0.51 |  |

#### Notes:

- 1. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25mm per side.

2. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-091-OT Rev H Sheet 2 of 2

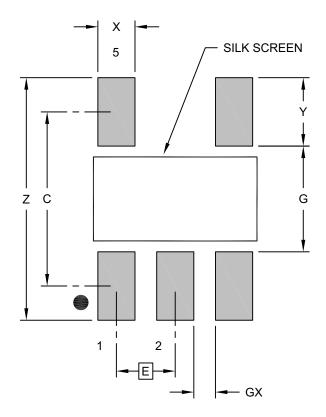

# 5-Lead Plastic Small Outline Transistor (OT) [SOT-23]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**RECOMMENDED LAND PATTERN**

|                         | MILLIMETERS |      |      |      |

|-------------------------|-------------|------|------|------|

| Dimension               | MIN         | NOM  | MAX  |      |

| Contact Pitch           | 0.95 BSC    |      |      |      |

| Contact Pad Spacing     | С           |      | 2.80 |      |

| Contact Pad Width (X5)  | Х           |      |      | 0.60 |

| Contact Pad Length (X5) | Υ           |      |      | 1.10 |

| Distance Between Pads   | G           | 1.70 |      |      |

| Distance Between Pads   | GX          | 0.35 |      |      |

| Overall Width           | Z           |      |      | 3.90 |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2091-OT Rev H

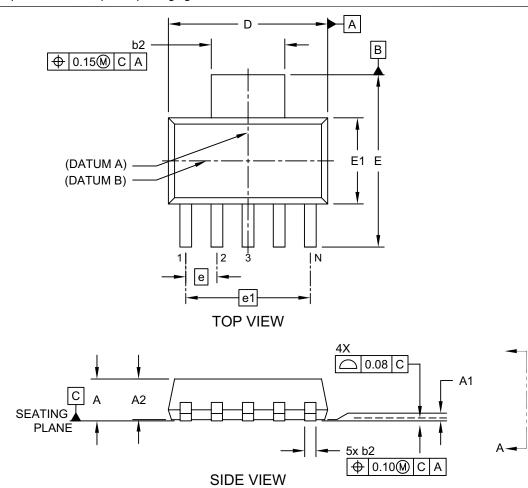

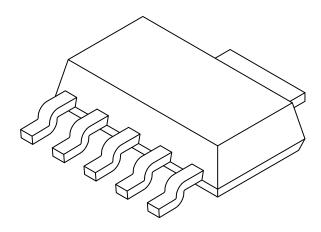

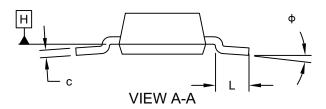

# 5-Lead Plastic Small Outline Transistor (DC) [SOT-223]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-137 Rev C Sheet 1 of 2

# 5-Lead Plastic Small Outline Transistor (DC) [SOT-223]

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                       | MILLIMETERS |      |          |      |  |

|-----------------------|-------------|------|----------|------|--|

| Dimension             | MIN         | NOM  | MAX      |      |  |

| Number of Leads       | N           |      | 5        |      |  |

| Lead Pitch            | е           |      | 1.27 BSC |      |  |

| Outside lead pitch    | e1          |      | 5.08 BSC |      |  |

| Overall Height        | Α           | 1.80 |          |      |  |

| Standoff              | A1          | 0.02 | 0.06     | 0.10 |  |

| Molded Package Height | A2          | 1.55 | 1.60     | 1.65 |  |

| Overall Width         | E           | 6.86 | 7.00     | 7.26 |  |

| Molded Package Width  | E1          | 3.45 | 3.50     | 3.55 |  |

| Overall Length        | D           | 6.45 | 6.50     | 6.55 |  |

| Lead Thickness        | С           | 0.24 | 0.28     | 0.32 |  |

| Lead Width            | b           | 0.41 | 0.46     | 0.51 |  |

| Tab Lead Width        | b2          | 2.95 | 3.00     | 3.05 |  |

| Foot Length           | L           | 0.91 | -        | -    |  |

| Lead Angle            | ф           | 0°   | -        | 10°  |  |

#### Notes:

Note:

- Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.127mm per side.

- 2. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-137 Rev C Sheet 2 of 2

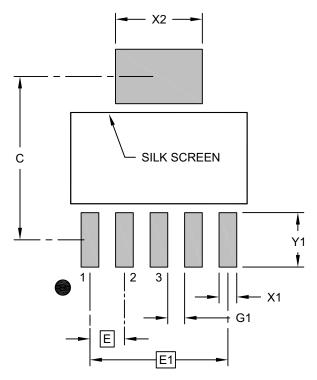

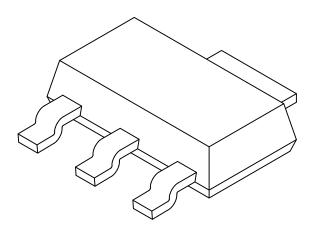

# 5-Lead Plastic Small Outline Transistor (DC) [SOT-223]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

| Units                      |    | MILLIMETERS |          |      |

|----------------------------|----|-------------|----------|------|

| Dimension Limits           |    | MIN         | NOM      | MAX  |

| Contact Pitch              | Е  |             | 1.27 BSC |      |

| Contact Pitch              | E1 | 5.08 BSC    |          |      |

| Contact Pad Spacing        | С  |             | 6.00     |      |

| Contact Pad Width (X5)     | X1 |             |          | 0.65 |

| Contact Pad Width          | X2 |             |          | 3.20 |

| Contact Pad Length (X6)    | Y1 |             |          | 2.00 |

| Distance Between Pads (X4) | G1 | 0.62        |          |      |

#### Notes:

- Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- 2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-2137 Rev B

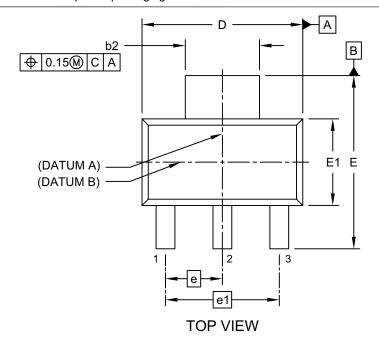

# 3-Lead Plastic Small Outline Transistor (DB) [SOT-223]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-032 Rev D Sheet 1 of 2

# 3-Lead Plastic Small Outline Transistor (DB) [SOT-223]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                 |    | MILLIMETERS |      |      |

|-----------------------|----|-------------|------|------|

| Dimension Limi        |    | MIN         | NOM  | MAX  |

| Number of Leads       | 3  |             |      |      |

| Lead Pitch            | е  | 2.30 BSC    |      |      |

| Outside lead pitch    | e1 | 4.60 BSC    |      |      |

| Overall Height        | Α  | ı           | ı    | 1.80 |

| Standoff              | A1 | 0.02        | ı    | 0.10 |

| Molded Package Height | A2 | 1.50        | 1.60 | 1.70 |

| Overall Width         | Е  | 6.70        | 7.00 | 7.30 |

| Molded Package Width  | E1 | 3.30        | 3.50 | 3.70 |

| Overall Length        | D  | 6.30        | 6.50 | 6.70 |

| Lead Thickness        | С  | 0.23        | 0.30 | 0.35 |

| Lead Width            | b1 | 0.60        | 0.76 | 0.84 |

| Tab Lead Width        | b2 | 2.90        | 3.00 | 3.10 |

| Foot Length           | Ĺ  | 0.75        | -    | -    |

| Lead Angle            | ф  | 0°          | -    | 10°  |

#### Notes:

- 1. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.127mm per side.

- 2. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-032 Rev D Sheet 2 of 2

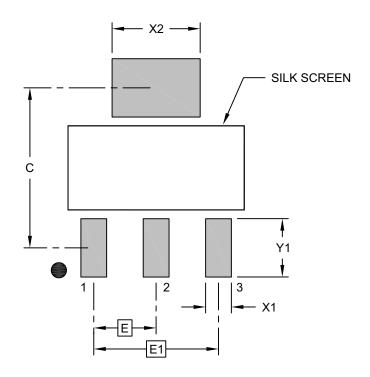

# 3-Lead Plastic Small Outline Transistor (DB) [SOT-223]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

| Units                   |    | MILLIMETERS |      |      |

|-------------------------|----|-------------|------|------|

| Dimension Limits        |    | MIN         | NOM  | MAX  |

| Contact Pitch E         |    | 2.30 BSC    |      |      |

| Contact Pitch           | E1 | 4.60 BSC    |      |      |

| Contact Pad Spacing     |    |             | 5.90 |      |

| Contact Pad Width (X3)  | X1 |             |      | 0.95 |

| Contact Pad Width       | X2 |             |      | 3.25 |

| Contact Pad Length (X4) | Y1 |             |      | 2.15 |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2032 Rev D

NOTES:

### APPENDIX A: REVISION HISTORY

# **Revision B (February 2023)**

- · Updated document layout.

- Added automotive qualification to Features and examples to Product Identification System.

- Updated Absolute Maximum Ratings to better describe the part.

- Note 6 (previously found in the table footnote of AC/DC Characteristics Table) was moved to Absolute Maximum Ratings and is now Note 1.

- Updated Section 6.0 "Packaging Information".

### **Revision A (November 2007)**

· Original Release of this Document.

| M   | CP'        | 182 | <b>4/N</b>    | ICP1 | <b>1824S</b> |

|-----|------------|-----|---------------|------|--------------|

| IVI | <b>U</b> I | IUZ | <b>-7/I</b> 1 |      | IUZTO        |

NOTES:

# PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO. X               | <del>x x x x/ xx xxx</del>                                                                                                                                                                                                                                                                                | Examples:                                                                                                                                                                                                                                                                    |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | put Feature Tolerance Temp. Package Qualification age Code                                                                                                                                                                                                                                                | a) MCP1824T-1202E/OT: Tape and Reel,<br>1.2V LDO Regulator, Fixed,<br>Extended Temperature,                                                                                                                                                                                  |

| Device:                  | MCP1824: 300 mA Low Dropout Regulator<br>MCP1824S: 300 mA Low Dropout Regulator                                                                                                                                                                                                                           | 5-Lead SOT-23 Package b) MCP1824T-2802E/OT: Tape and Reel, 2.8V LDO Regulator, Fixed, Extended Temperature,                                                                                                                                                                  |

| Tape and Reel<br>Option: | T = Tape and Reel <sup>(1)</sup>                                                                                                                                                                                                                                                                          | 5-Lead SOT-23 Package<br>c) MCP1824-ADJE/OTVAO: Tape and Reel,<br>Adjustable LDO Regulator,                                                                                                                                                                                  |

| Output Voltage *:        | 08 = 0.8V "Standard"<br>12 = 1.2V "Standard"<br>18 = 1.8V "Standard"<br>25 = 2.5V "Standard"                                                                                                                                                                                                              | Extended Temperature, 5-Lead SOT-23 Package, Automotive Qualified d) MCP1824T-3E02E/DC: Tape and Reel,                                                                                                                                                                       |

|                          | 28 = 2.8V "Custom"<br>30 = 3.0V "Standard"<br>3E = 3.35V "Custom"<br>33 = 3.3V "Standard"                                                                                                                                                                                                                 | 3.35V LDO Regulator, Fixed, Extended Temperature, 5-Lead SOT-223 Package e) MCP1824T-1802E/DC: Tape and Reel,                                                                                                                                                                |

|                          | 50 = 5.0V "Standard"  ADJ = Adjustable Output Voltage** (MCP1824 Only)  * Contact factory for other output voltage options  ** When ADJ is used, the "extra feature code" and "tolerance"                                                                                                                 | 1.8V LDO Regulator, Fixed, Extended Temperature, 5-Lead SOT-223 Package                                                                                                                                                                                                      |

| Extra Feature<br>Code:   | columns do not apply. Refer to examples.  0 = Fixed                                                                                                                                                                                                                                                       | f) MCP1824T-0802E/DCVAO: Tape and Reel,<br>0.8V LDO Regulator, Fixed,<br>Extended Temperature,<br>5-Lead SOT-223 Package,                                                                                                                                                    |

| Tolerance:               | 2 = 2.5% (Standard)                                                                                                                                                                                                                                                                                       | Automotive Qualified g) MCP1824ST-2502E/DB: Tape and Reel, 2.5V LDO Regulator, Fixed,                                                                                                                                                                                        |

| Temperature:             | $E = -40^{\circ}C \text{ to } +125^{\circ}C \text{ (Extended)}$                                                                                                                                                                                                                                           | Extended Temperature, 3-Lead SOT-223 Package h) MCP1824ST-3302E/DB: Tape and Reel,                                                                                                                                                                                           |

| Package Type:            | DB = Plastic Small Transistor Outline, SOT-223, 3-Lead DC = Plastic Small Transistor Outline, SOT-223, 5-Lead OT = Plastic Small Transistor Outline, SOT-23, 5-Lead                                                                                                                                       | 3.3V LDO Regulator, Fixed, Extended Temperature, 3-Lead SOT-223 Package                                                                                                                                                                                                      |

|                          | Note 1: ADJ (Adjustable) only available in 5-Lead version.  Note 2: Solder Composition for 5-Lead SOT-23 package (OT) may be NiPbAu or Matte Tin.                                                                                                                                                         | i) MCP1824ST-5002E/DB: Tape and Reel,<br>5.0V LDO Regulator, Fixed,<br>Extended Temperature,<br>3-Lead SOT-223 Package                                                                                                                                                       |

| Qualification***:        | (Blank) = Standard Part VAO = Automotive AEC-Q100 Qualified  *** Currently available VAO variants are: MCP1824T-1202E/OTVAO, MCP1824T-ADJE/OTVAO and MCP1824T-0802E/DCVAO. Contact your local Microchip sales office to request automotive qualified variants for other package types or voltage options. | Note 1: Tape and Reel identifier only appears in the catalog part number description. This identifier is used for ordering purposes and is not printed on the device package. Check with your Microchip Sales Office for package availability with the Tape and Reel option. |

NOTES:

#### Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not

mean that we are guaranteeing the product is "unbreakable" Code protection is constantly evolving. Microchip is committed to

continuously improving the code protection features of our products.

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at <a href="https://www.microchip.com/en-us/support/design-help/client-support-services">https://www.microchip.com/en-us/support/design-help/client-support-services</a>.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, TrueTime, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.